FAIRCHILD FDD8424H Manual

Contents

1. Typical Characteristics Q2 P Channel r 25 C unless otherwise noted 10 2000 gt Ciss u 1000 II 2 8 LE re 5 ID Coss u 6 u H E tc lt 3 E aa S lt o n Ciss o 100 HI o E 2 f 1MHz i Vas 0V eo o 0 30 0 4 8 12 16 20 0 1 1 10 40 Qy GATE CHARGE nC Vps DRAIN TO SOURCE VOLTAGE V Figure 20 Gate Charge Characteristics Figure 21 Capacitance vs Drain to Source Voltage 30 25 ES E M 10 5 e Ty 25 C ui 4 o 2 ui Ty 125 C o o z z Ka2. 2000 1000 Ciss T 2 LU o E Coss o lt 100 o f 1MHz Vas ON Crss 30 0 1 1 10 40 Vos DRAIN TO SOURCE VOLTAGE V Figure8 Capacitance vs Drain to Source Voltage 30 z 25 Fe Limited by Package E amp 20 tc 5 O 15 z amp 10 5 Rouc 4 1 C W 0 25 50 75 100 125 150 Te CASE TEMPERATURE C Figure10 Maximum Continuous Drain Current vs CaseTemperature 10000 3 Vaa 10V FOR TEMPERATURES m Gs E ABOVE 25 C DERATE PEAK O 1000 CURRENT AS FOLLOWS e r D n Tei 1 los 25 D L J E Tc 25 C e E 100 x a SINGLE PULSE F He 4 1 C W a 10 Linn rit a 10 10 10 10 10 10 10 t PULSE WIDTH s Figure12 Single Pulse Maximum Power Dissipation 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIUS1L19MOQd Iouupu rd 8 N IENA Hrergadd

3. Typical Characteristics Q1 N Channel r 25 c unless otherwise noted 60 3 0 I Vas 4 0V o PULSE DURATION Bus 50 A DUTY CYCLE 0 5 Ves 10V p 25 40 PULSE DURATION 80us Si z DUTY CYCLE 0 5 MAX QU 29 ZS Ves 4 5V NE T 30 zu 3 Ves 3 5V so S as 5 ES 15 x 20 zo tc o a o S 40 E 10 Ves 3 0V z Vos 10V 5 0 0 5 0 1 2 3 4 0 10 20 30 40 50 60 Vps DRAIN TO SOURCE VOLTAGE V Ip DRAIN CURRENT A Figure 1 On Region Characteristics Figure2 Normalized On Resistance vs Drain Current and Gate Voltage 18 50 u lp 2 9A Ib 9A PULSE DURATION 80us Z 1 6 Ves 10V T DUTY CYCLE 0 5 MAX E 2 u 40 o at 1 4 e z Ty 125 C NZ 2 5 39 12 rH 30 o D H S tc ae SP 9o 10 ES ow o 20 Lr tc z 08 2 o 2 06 10 75 50 25 0 25 50 75 100 125 150 2 4 6 8 10 Ty JUNCTION TEMPERATURE C Vas GATE TO SOURCE VOLTAGE V Figure3 Normalized On Resistance Figure 4 On Resistance vs Gate to vs Junction Temperature Source Voltage 60 60 PULSE DURATION 80us z Ves 0V 50 L DUTY CYCLE 0 5 MAX 10 Vps 5V te F 40 c T 150 C z 2 1 iu o T z 30 z B a 01 Ty 25 C z ul 20 o tc D a Ty 1509C Ty 25 C a e 0 01 10 Ty 55 C Ty 55 C T 0 0 001 1 5 2 0 2 5 3 0 3 5 4 0 4 5 0 0 0 3 0 6 0 9 1 2 1 5 Ves GATE TO

4. Typical Characteristics Q1 N Channel r 25 C unless otherwise noted 2 4 DUTY CYCLE DESCENDING ORDER a TT D 05 zo 0 2 Du Lo 01 y Eu 0 05 ms 04 002 DM s 0 01 au i ta l zz t ET S gt tj NOTES SINGLE PULSE DUTY FACTOR D bit 0 01 Rage 4 1 CW PEAK T Pom X Zouc X Rouc Tc 0 005 L LLLLLI i 10 10 10 10 10 10 10 t RECTANGULAR PULSE DURATION s Figure 13 Transient Thermal Response Curve 2007 Fairchild Semiconductor Corporation 6 www fairchildsemi com FDD8424H Rev C LAASOW 49u31 L1 MOd Iouupu rd 8 N IENA Hrergadd 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIUS91L19MOQd Iouupu rd 8 N IENA Hrergadd 40 PULSE DURATION 80us DUTY CYCLE 0 5 MAX 30 20 Ip DRAIN CURRENT A 10 Vos 3V 0 1 2 3 4 Vps DRAIN TO SOURCE VOLTAGE V Figure 14 On Region Characteristics 1 6 lp 6 5A Ves 10V 1 4 1 2 1 0 0 8 NORMALIZED DRAIN TO SOURCE ON RESISTANCE 0 6 75 50 25 0 25 50 75 100 125 150 Ty JUNCTION TEMPERATURE C Figure 16 Normalized On Resistance vs Junction Temperature 40 PULSE DURATION 80us DUTY CYCLE 0 5 MAX

5. e Vos 5V ch o Ip DRAIN CURRENT A N eo 1 2 3 4 5 Mee GATE TO SOURCE VOLTAGE V Figure 18 Transfer Characteristics Typical Characteristics Q2 P Channel r 25 C unless otherwise noted 3 0 T Ves 3V I w es PULSE DURATION 80us m DUTY CYCLE 0 5 MAX Z 2 5 4 5 Vas o a S 2 0 z NS i915 co 228 z o o 1 0 F z Sos 0 10 20 30 40 Ip DRAIN CURRENT A Figure 15 Normalized on Resistance vs Drain Current and Gate Voltage 160 PULSE DURATION 80us ma DUTY CYCLE 0 5 MAX 120 rs Ip 6 5A EZ ze an Ty 125 C x go 80 OD D ae sz ZO 40 a i Ty 25 C 7 0 2 4 6 8 10 Mee GATE TO SOURCE VOLTAGE V Figure 17 On Resistance vs Gate to Source Voltage 40 c T zs Ves 0V 10 F z DI is 5 1 o Ty 25 C Le 10 au Ta 150 C 0 Ty 55 C tc DI m 0 01 tc EI 0 001 0 0 0 3 0 6 0 9 1 2 1 5 Vsp BODY DIODE FORWARD VOLTAGE V Figure 19 Source to Drain Diode Forward Voltage vs Source Current 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIUS1L19MOQd Iouupu rd 8 N IENA Hrergadd

6. 1 Life support devices or systems are devices or systems which a are intended for surgical implant into the body or b support or sustain life and c whose failure to perform when properly used in accordance with instructions for use provided in he labeling can be reasonably expected to result in a significant 2 A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness injury of the user PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status Definition Advance Information Formative or In Design This datasheet contains the design specifications for product development Specifications may change in any manner without notice Preliminary No Identification Needed First Production Full Production This datasheet contains preliminary data supplementary data will be published at a later date Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design This datasheet contains final specifications Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design Obsolete Not In Production This datasheet contains specifications on a product that has been emiconductor The datasheet is printed

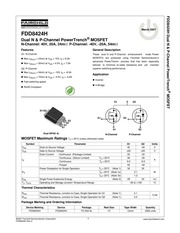

7. EEN FAIRCHILD Ee SEMICONDUCTOR March 2007 Dual N amp P Channel PowerTrench MOSFET N Channel 40V 20A 24mQ P Channel 40V 20A 54mQ Features General Description Q1 N Channel These dual N and P Channel enhancement mode Power m Max rps on 24mQ at Veg 10V Ip 9 0A MOSFETs are produced using Fairchild Semiconductor s advanced PowerTrench process that has been especially tailored to minimize on state resistance and yet maintain Q2 P Channel superior switching performance W Max rps on 54mQ at Veg 10V Ip 6 5A W Max eau 30mQ at Ves 4 5V lp 7 0A Application W Max eau 70MQ at Ves 4 5V lp 5 6A OR W Inverter W Fast switching speed m H Bridge W RoHS Compliant D1 D2 D1 D2 G1 G2 S1 S2 Dual DPAK 4L N Channel P Channel MOSFET Maximum Ratings Tc 25 C unless otherwise noted Symbol Parameter Q1 Q2 Units Vps Drain to Source Voltage 40 40 V Vas Gate to Source Voltage 20 20 V Drain Current Continuous Package Limited 20 20 I Continuous Silicon Limited Tc 25 C 26 20 A B Continuous Ta 25 C 9 0 6 5 Pulsed 55 40 Power Dissipation for Single Operation Tc 25 C Note 1 30 35 Pp TA 25 C Note 1a 3 1 W Ta 25 C Note 1b 3 Eas Single Pulse Avalanche Energy Note 3 29 33 mJ Ty Tera Operating and Storage Junction Temperature Range 55 to 150 C Thermal Characteristics Roc The

8. 10V Ip 9 0A 19 24 Ves 4 5V Ins 7 0A Q1 23 30 Le Ves 10V Ip 9 0A Ty 125 C 29 37 DS on Static Drain to Source On Resistance Vas 10V Ip 6 5A 42 54 mo Ves 4 5V Ip 5 6A Q2 58 70 Ves 10V Ip 6 5A Ty 125 C 62 80 Vps 5V Ip 9 0A Q1 29 grs Forward Transconductance Vps 5V Ip 6 5A Q2 13 S Dynamic Characteristics Q1 750 1000 Ci Input Capacitance Q1 F ss p P Vps 20V Vas OV f 1MHZ Q2 1000 1330 P Q1 115 155 Coss Output Capacitance Q2 Q2 140 185 pF Vos 20V Vas OV f 1MHZ Q1 75 115 Criss Reverse Transfer Capacitance Q2 75 115 pF gt Q1 1 1 Rg Gate Resistance f 1MHz Q2 3 3 Q Switching Characteristics Q1 7 14 td on Turn On Delay Time Q1 Q2 7 14 ns EE Von 20V Ip 9 0A ai 13 24 t Rise Time Vas 10V Reen 62 Q2 3 10 ds td off Turn Off Delay Time Q2 gt 2n T ns Von 20V Ip 6 5A ES E gt i Vas 10V Regen 62 lr Fall Time GS G Q2 3 10 ns Q1 14 20 Damon Total Gate Charge Q1 Q2 17 24 nC Vas 10V Vpp 20V Ip 9 0A To 23 Qgs Gate to Source Charge Q2 30 nC Q2 in Miller Ves 10V Vpp 20V Ip 6 5A Q1 3 2 Qoa Gate to Drain Miller Charge Gs gt VDD lo Q2 36 nC 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIUS1L19MOQd Iouupu rd 8 N IENA Hrergadd Electrical Characteristics Ty 25 C unless otherwise noted by the us

9. S i E X T E 1 0 001 0 01 0 1 1 10 100 25 50 75 100 125 150 tav TIME IN AVALANCHE ms Ty CASE TEMPERATURE C Figure 22 Unclamped Inductive Figure 23 Maximum Continuous Drain Switching Capability Current vs Case Temperature 100 10000 10us Vas 10V T SN tc FOR TEMPERATURES Lr IPL D A E ABOVE 25 C DERATE PEAK amp 10 LL It 100us 1000 CURRENT AS FOLLOWS amp BERge 2 4 Tl E 150 Tc 2 THIS AREA IS FEIT e E de m z LIMITED BY rason so TA AE 9 Ny Sims amp Tc s 259C a 1 SINGLE PULSE t 100 m Ty MAX RATED tI 10ms a I Rac 3 5 C W lee E SINGLE PULSE Tg 25 C E Ren 3 5 C W 0 1 ii 10 L Lou iua ciun 1 10 80 10 10 10 10 10 10 10 10 10 Vps DRAIN to SOURCE VOLTAGE V t PULSE WIDTH s Figure 24 Forward Bias Safe Figure 25 Single Pulse Maximum Operating Area Power Dissipation 2007 Fairchild Semiconductor Corporation 9 www fairchildsemi com FDD8424H Rev C LAASOW 49u31 L1 MOd JeUUBYD d 8 N IENA Hrergadd Typical Characteristics Q2 P Channel r 25 C unless otherwise noted RR 1 DUTY CYCLE DESCENDING ORD

10. discontinued by Fairchild for reference information only Rev 124 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIUS1LI9MOQ ISUUEUI d 8 N IENQ Hrzrgadd

11. ER LU a m D 05 0 2 Y UI N z E ui 0 05 Pp m SE 0 01 E a D ra ss t Le S NOTES z DUTY FACTOR D Hits 0 01 SINGLE PULSE PEAK T Pom X Zouc X Rouc Tc A O Ryc 3 5 C W 0 005 LELT I 105 10 10 10 10 10 10 t RECTANGULAR PULSE DURATION s Figure 26 Transient Thermal Response Curve 2007 Fairchild Semiconductor Corporation 10 www fairchildsemi com FDD8424H Rev C LAASOW 49u31 L1 MOd Iouupu rd 8 N IENA Hrergadd d d 6 25 D XX c a E LAND PATTERN RECOMMENDATION NOTES UNLESS OTHERWISE SPECIFIED A THIS PACKAGE CONFORMS TO JEDEC TO 252 ISSUE E VARIATION AD DATED JUNE 2004 B ALL DIMENSIONS ARE IN MILLIMETERS C DIMENSIONS ARE EXCLUSIVE OF BURRS MOLD FLASH AND TIE BAR EXTRUSIONS D HEAT SINK TOP EDGE COULD BE IN CHAMFERD CORNERS OR EDGE PROTRUSION E DIMENSIONS AND TOLERANCES PER ASME Y14 5M 1994 2007 Fairchild Semiconductor Corporation 11 www fairchildsemi com FDD8424H Rev C LAASOW QUHIUS1L19MOQd ISUUEUT d 8 N IENA Hrergadd LU FAIRCHILD E SEMICONDUCTOR TRADEMARKS LIFE SUPPORT POLICY As used herein The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks ACEx HiSeC Programmable Active Droop TinyLogic Across the board Around the world i Lo QFET TINYOPTO ActiveArrayT

12. M ImpliedDisconnect QS TinyPower Bottomless InteliMAX QT Optoelectronics TinyWire Build it Now ISOPLANARTM Quiet SeriesTM TruTranslation CoolFETTM MICROCOUPLERTM RapidConfigureTM uSerDes M CROSSVOLT MicroPak RapidConnect UHC CTL MICROWIRE ScalarPump UniFET Current Transfer Logic MSXTM SMART START M VCXTM DOMETM MSXPro SPM Wire E CMOSTM OCXTM STEALTHTM EcoSPARK OCXPro SuperFET EnSigna OPTOLOGIC SuperSOT 3 FACT Quiet Series OPTOPLANAR SuperSOT 6 FACT PACMAN SuperSOT 8 FAST POP SyncFET FASTr Power220 TCM FPS Power247 The Power Franchise FRFET PowerEdge TM GlobalOptoisolator PowerSaver TinyBoost GTO PowerTrench TinyBuck DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY FUNCTION OR DESIGN FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS NOR THE RIGHTS OF OTHERS THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD S WORLDWIDE TERMS AND CONDITIONS SPECIFICALLY THE WARRANTY THEREIN WHICH COVERS THESE PRODUCTS FAIRCHILD S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION

13. SOURCE VOLTAGE V Vsp BODY DIODE FORWARD VOLTAGE V Figure 5 Transfer Characteristics Figure6 Sourceto Drain Diode Forward Voltage vs Source Current 2007 Fairchild Semiconductor Corporation 4 www fairchildsemi com FDD8424H Rev C LAASOW 49u31 L1 MOd Iouupu rd 8 N IENA Hrergadd 10 S S 9 a8 m l Q u 6 o D 2 a 4 o F H z 2 o o 7 Q0 16 Qg GATE CHARGE nC Figure 7 Gate Charge Characteristics 30 T z Ty 25 C u 10 Lu LHN i HHHH tc 2 o H I o z d Ty 125 C lt E 1 0 001 0 01 0 1 1 10 100 tav TIME IN AVALANCHE ms Figure9 Unclamped Inductive Switching Capability 100 lt ke H D o THIS AREA IS ELI S K z LIMITED BY ros KIN TL a SINGLE PULSE SE ime Ty MAX RATED Six Ryo 4 1 C W SF 10ms Tc 25 C DC 0 1 1 10 80 Vps DRAIN to SOURCE VOLTAGE V Figure 11 Forward Bias Safe Operating Area Typical Characteristics Q1 N Channel r 25 C unless otherwise noted

14. er s board design Q1 Q2 D 00000 00000 2 Pulse Test Pulse Width lt 300us Duty cycle lt 2 0 a 40 C W when mounted on a1in pad of 2 oz copper Scale 1 1 on letter size paper a 40 C W when mounted on a1in padof 2 oz copper Scale 1 1 on letter size paper b 96 C W when mounted on a minimum pad of 2 oz copper b 96 C W when mounted on a minimum pad of 2 oz copper 8 Starting Ty 25 C N ch L 0 3mH las 14A Vpp 40V Vag 10V P ch L 0 3mH las 15A Vpp 40V Vas 10V Symbol Parameter Test Conditions Type Min Typ Max Units Drain Source Diode Characteristics n Ves OV ls 9 0A Note 21 Q1 0 87 1 2 Vsp Source to Drain Diode Forward Voltage Vas OV ls 6 5A Note 2 Q2 088 42 V Q1 Q1 25 38 t Reverse Recovery Time ns E ee I 9 0A di dt 100A s Q2 29 44 Q2 Q1 19 29 Qr Reverse Recovery Charge IF 6 5A di dt 100A s Q2 29 44 nC Notes 1 Roja is determined with the device mounted on a 1in pad 2 oz copper pad on a 1 5 x 1 5 in board of FR 4 material Roy is guaranteed by design while Roca is determined 2007 Fairchild Semiconductor Corporation FDD8424H Rev C www fairchildsemi com LAASOW QUIU91L19MOQd Iouupu rd 8 N IENA Hrergadd

15. rmal Resistance Junction to Case Single Operation for Q1 Note 1 4 1 CN Roc Thermal Resistance Junction to Case Single Operation for Q2 Note 1 3 5 Package Marking and Ordering Information Device Marking Device Package Reel Size Tape Width Quantity FDD8424H FDD8424H TO 252 4L 13 12mm 2500 units 2007 Fairchild Semiconductor Corporation 1 www fairchildsemi com FDD8424H Rev C LAASOW QU9U91L19MOQd Iouupu rd 8 N IENA Hrergadd Electrical Characteristics T 25 C unless otherwise noted Symbol Parameter Test Conditions Type Min Typ Max Units Off Characteristics Ip 250uA Vas OV Q1 40 BVpss Drain to Source Breakdown Voltage Ip 250uA Vas OV Q2 40 V ABVpss Breakdown Voltage Temperature Ip 250p A referenced to 25 C Q1 34 mV C AT Coefficient Ip 250uA referenced to 25 C Q2 32 Vps 32V Mee 0V Q1 1 Ipss Zero Gate Voltage Drain Current Vos 32V Vag OV Q2 1 uA Q1 100 nA lass Gate to Source Leakage Current Ves 20V Vps OV Q2 100 SA On Characteristics Vas Vos lp 2504A Q1 1 1 7 3 Vesith Gate to Source Threshold Voltage Vas Vps Ip 250A Q2 4 1 6 3 V AVGs th Gate to Source Threshold Voltage Ip 250pA referenced to 25 C Q1 5 3 mV C AT Temperature Coefficient Ip 250uA referenced to 25 C Q2 4 8 Ves

Download Pdf Manuals

Related Search

FAIRCHILD FDD8424H Manual