ANALOG DEVICES AD6623handbookRev A

Contents

1. EE KEY ROSS 28 Driving Multiple TSP Serial Ports 43 Output Clip Detection 1e amara ted cn OE REA deta eigene 28 USING THE AD6623 TO PROCESS TWO UMTS CARRIERS Cascading Multiple AD66238 28 WITH 24 OUTPUT RATE Ts oo Ran CEDERE QUEM 44 Selection of Real and Complex Data Types 29 DUOSTVIE ue css A SEN Le RT pam eben QA ATE 44 SYNCHRONIZATION orenean EEEN TE i m hn 29 Configuring the AD6623 44 Hold Off Counters and Shadow Registers 29 AD6623 Register Configuration 44 Start d RR eec og Suen a te Ee en eee 29 THERMAL MANAGEMENT 0000 cee n 46 Start with No Syne vies wer e eph RUE RENAL n 29 OUTLINE DIMENSIONS s esses ee 47 Revision HOR Pe Se nd wae ene AMER ee qe 48 2 REV A AD6623 PRODUCT DESCRIPTION The AD6623 is a 4 channel Transmit Signal Processor TSP that creates high bandwidth data for Transmit Digital to Analog Converters TxDACs from baseband data provided by a Digi tal Signal Processor DSP Modern TxDACs have achieved sufficiently high sampling rates analog bandwidth and dynamic range to create the first Intermediate Frequency IF directly The AD6623 synthesizes multicarrier and multistandard di2. aos eset o Ste seed 39 PROGRAMMABLE RAM COEFFICIENT FILTER RCF 16 0xn02 NCO Frequency eerie eee eect ae 39 OVERVIEW OF THE RCF BLOCKS 17 0xn03 NCO Frequency Update Hold Off Counter 39 INTERPOLATING FIR FILTER 18 0xn04 NCO Phase 39 Channel RCF Control Registers 20 0xn05 NCO Phase Offset Update Hold Off Counter 39 PSK MODULATOR Exe EE Dane ee Me 20 02006 CIC Scale ees agente dit aren eee 39 TA A DOSPK Modulation 21 0xn07 CIC2 Decimation 1 1 39 8 PSK Modulation r a ayunaspa pupas eee nee 21 0xn08 CIC2 Interpolation 1 Leica 1 39 30 8 8 PSK Modulation 21 0509 CICS Interpolation Dee es 39 MSE Look Up Table ES RR UE 22 0xn0A Number of RCF Coefficients 1 39 GMSK Look Up Table serok Rau CREER ad AK 22 0xn0B RCF Coefficient Offset 39 OPSK Look Up Table iz 9 ei hand Foe Oo ERA REY RAP 22 0xn0C Channel Mode Control 1 39 PHASE EQUALIZER a aaa quas ka baha aen AS

3. 0 1000 2000 3000 4000 5000 6000 7000 8000 9000 10000 kHz Figure 44 RCF and CIC Frequency Response for WBCDMA USING THE AD6623 TO PROCESS TWO UMTS CARRIERS WITH 24x OUTPUT RATE Overview The AD6623 may be used to process two UMTS carriers each with an output rate of 24x i e 92 16 MSPS The AD6623 configuration used to accomplish this consists of using two pro cessing channels in parallel to process each UMTS carrier The ideology behind the parallel processing approach is that each channel operates on half of the input samples processing every other sample The reason is that the serial input data rate is limited to 3 25 MSPS for 16 bit I and 16 bit Q data 104 MSPS 32 The first channel of each pair begins processing the first input sample immediately The second channel begins processing after a specific delay so that the two channels essentially will be operating 180 degrees out of phase with each other Since each channel processes only half the input samples and thus receives input data at half the original rate each channel has twice the original amount of time available for processing This in turn makes available twice the original number of taps resulting in much improved digital filtering capability To maximize the number of available FIR filter taps the highest possible input rate should be used 44 Therefore this application note assumes an input sample rate of 3 84

4. 21 The pass band droop of CIC5 should be calculated using this equation and can be compensated for in the RCF stage The gain should be calculated from the CIC scaling section above Programming Guidelines for AD6623 CIC Filters The values M cico 1 2 1 can be independently pro grammed for each channel at locations 0xn07 0xn08 While these control registers are nine bits and 12 bits wide respec tively M cic 1 and L crc2 1 should be confined to the ranges shown by Table XIII according to the interpolation factor of the CIC5 Exceeding the recommended guidelines may result in overflow for input sequences at or near full scale While rela tively large ratios of L cic M cic allow for the larger overall interpolations with minimal power consumption 2 should be minimized to achieve the best overall image rejection 26 As an example consider an input from the CIC5 whose bandwidth is 0 0033 of the CIC5 rate centered at baseband Interpolation by a factor of five reveals five images as shown below 10 dB 4 3 2 1 0 1 2 3 Figure 31 Unfiltered rCIC2 Images The rCIC2 rejects each of the undesired images while passing the image at baseband The images of a pure tone at channel center DC are nulled perfectly but as the bandwidth increases the rejection is diminished The lower band edge of the first image always has the least rejection In this example the rCI

5. 0 3 V to 5 V 5 V Tolerant Output Voltage Swing 0 3 V to VDDIO 0 3 V Load Capacitance 200 pF Junction Temperature Under Bias 125 C Operating Temperature 40 C to 85 C Ambient Storage Temperature Range 65 C to 150 C Lead Temperature 5 sec 280 Stresses greater than those listed above may cause permanent damage to the device These are stress ratings only functional operation of the devices at these or any other conditions greater than those indicated in the operational sections of this specification is not implied Exposure to absolute maximum rating conditions for extended periods may affect device reliability THERMAL CHARACTERISTICS 128 Lead MQFP with Internal Heat Spreader 28 1 C W no airflow 22 6 C W 200 airflow 20 5 C W 400 lfpm airflow 196 Lead BGA 6j4 26 3 C W no airflow O14 22 C W 200 Ifpm airflow Thermal measurements made in the horizontal position on a 4 layer board EXPLANATION OF TEST LEVELS I 100 Production Tested II 100 Production Tested at 25 C and Sample Tested at Specified Temperatures III Sample Tested Only IV Parameter Guaranteed by Design and Analysis V Parameter is Typical Value Only ORDERING GUIDE Model Temperature Range Package Description Package Option AD6623AS 40 C to 85 C Ambient 128 Lead MQFP

6. OSS 7 aed Sneed em MOX ERAS 33 ABSOLUTE MAXIMUM RATINGS 10 Mu lticarnier Scalig oes vv y SESE ae ECKE RW 33 THERMAL CHARACTERISTICS 10 Single Carrier Scalig sese ek EC 33 EXPLANATION OF TEST LEVELS 10 MICROPORT INTERFACE 34 ORDERING GUIDE PAE E 10 Micr port Control isisa ae aulas pacte ERE E a RR eet 34 PIN CONFIGURATION 128 Lead MQFP 11 EXTERNAL MEMORY MAP 34 128 PIN FUNCTION DESCRIPTION 12 Intel Nonmultiplexed Mode INM 35 PIN CONFIGURATION 196 Lead CSPBGA 13 Motorola Nonmultiplexed Mode 35 196 PIN FUNCTION DESCRIPTION 14 External Address 7 Upper Address Register UAR 35 POWERSUPPLY s taa T dre NU RU QU nda PAN 14 External Address 6 Lower Address Register LAR 35 INPUTS cee Re oak Sei es PE heen RR MERE CoS 14 External Address 5 35 CONTROL ee we nena REY 14 External Address 4 Sleep eS ee XY x AS 36

7. Switching Characteristics sciri TCLK to TSCLK Delay divide by 1 Full IV 4 10 5 ns tpscLKH TCLK to TSCLK Delay for any other divisor Full IV 5 13 ns tDSCLKL TCLK to J SCLK Delay divide by 2 or even number Full IV 3 5 9 ns tpscLKLL CLK to Delay divide by 3 or odd number Full IV 4 10 ns Channel is Self Framing tssDIo SDIN to TSCLK Setup Time Full IV 1 7 ns SDIN to TSCLK Hold Time Full IV 0 ns tpsEO0A TSCLK to SDFO Delay Full IV 0 5 3 5 05 Channel is External Framing tssFIO SDFI to TSCLK Setup Time Full IV 2 ns THSFIO SDFI to SCLK Hold Time Full IV 0 05 15800 SDIN to TSCLK Setup Time Full IV 2 ns tHSDIO SDIN to TSCLK Hold Time Full IV 0 ns tpsFooB TSCLK to SDFO Delay Full IV 0 5 3 ns Slave Mode Serial Port Timing Requirements SCS 1 Switching Characteristics SCLK Period Full IV 2 X terx ns tscLKL SCLK Low Time Full IV 3 5 ns tscLKH SCLK High Time Full IV 3 5 ns Channel is Self Framing tsspH SDIN to TSCLK Setup Time Full IV 1 ns tyspH SDIN to TSCLK Hold Time Full IV 2 5 ns tpsFo1 TSCLK to SDFO Delay Full IV 4 10 ns Channel is External Framing tssEI SDFI to TSCLK Setup Time Full IV 2 ns SDFI to TSCLK Hold Time Full IV 1 ns SDIN TSCLK Setup Time Full IV 1 ns SDIN to TSCLK Hold Time Full IV 2 5 ns tpsFo1 to SDFO Delay Full IV 10 ns NOTES All Timing Specifications valid over VDD range of 2 375 V to 2 675 V and VDDIO range of 3 0 V to 3 6 V 2Croap

8. The ramp unit when bypassed will have exactly 0 dB of gain and can be ignored When in use the gain is dependant on what value 15 stored in the last valid RMEM location RMEM words are 14 bits 0 1 so when the value is positive full scale the gain is about 0 0005 dB probably neglectable The RCF coefficients should be normalized to positive full scale This will yield the greatest dynamic range The RCF is equipped with an output scaler that ranges from 0 dB to 18 06 dB below full scale in 6 02 dB steps This attenuation can be used par tially compensate for filter gain in the RCF For example if the maximum gain of the RCF coefficients is 11 26 dB the RCF coarse scale should be set to 2 12 04 dB This yields an RCF output level and fine scale input level of 0 78 dB 11 26 12 04 0 78 24 The fine scale unit is left to turn 0 78 dB level into a 5 59 dB level This requires a gain of 4 81 dB which corresponds to a 14 bit 0 2 scale value of 1264h All subsequent rescalings during chip operation should be relative to this maximum 5 59 0 78 4 81 25 481 floor ho 2 x 12644 26 Finally as described in the RCF section there may be a worst case peak of a phase that is larger than the channel center gain In the preceding example if the worst case to channel center ratio is larger than 4 59 dB potentially overflowing the RCF then the RCF_ Coarse Scale should be reduced by one and the CIC S

9. Bit 3 Reserved Bit 2 High enables Serial Time Slot Syncs not available in FIR Mode Bit 1 High enables Power Ramp coefficient interpolation Bit 0 High enables the Power Ramp 40 0xn17 Power Ramp Length 0 This is the length of the ramp for Mode 0 minus one 0xn18 Power Ramp Length 1 This is the length of the ramp for Mode 1 minus one Setting this to zero disables dual ramps 0xn19 Power Ramp Rest Time This is the number of RCF output samples to rest for between ramp down and a ramp up 0xn1A 0xn1F Unused 0xn20 0xn3F Data Memory This group of registers contain the RCF Filter Data See the RCF section for additional details 0xn40 0xn7F Power Ramp Coefficient Memory This group of registers contain the Power Ramp Coefficients See the Power Ramp section for additional details 0xn80 0xnFF Coefficient Memory This group of registers contain the RCF Filter Coefficients See the RCF section for additional details PSEUDOCODE Write Pseudocode Void Write Micro ext address int data Main This code shows the programming of the NCO frequency register using the Write Micro function defined above The variable address is the External Address A 2 0 and data is the value to be placed in the external interface register Internal Address 0x102 channel 1 Holding registers for NCO byte wide access data int d3 d2 d1 d0 word CO_FREQ 0x1BEFEFFF write Chan rite

10. Ch A RCF Phase EQ Coef2 0x112 16 15 0 Ch A RCF MPSK Magnitude 0 0 113 16 15 0 Ch RCF Magnitude 1 0 114 16 15 0 Ch RCF Magnitude 2 0 115 16 15 0 Ch RCF Magnitude 3 0 116 8 7 Reserved 6 Ch A Serial Data Frame Select 0 Serial Data Frame Request 1 Serial Data Frame End 20 Figure 21 16 Phase Modulations REV A AD6623 All of these phase locations are represented in rectangular coor dinates by only four unique magnitudes in the positive and negative directions These four values are read from four channel registers that are programmed according to the following table which gives the generic formulas and a specific example The example is notable because it is only 0 046 dB below full scale and the 16 bit quantization is so benign at that magnitude that the rms error is better than 122 dBc It is also worth noting that because none of the phases are aligned with the axes magnitudes slightly beyond 0 16 dB above full scale are achievable Table VI Program Registers Channel Register Magnitude M Magnitude E 0x7F53 0x12 3 16 0x7CE1 0x13 M 3 cos 377 16 0x69DE 0x14 M 3 5 16 0x46BD 0x15 M 3 cos 777 16 0x18D7 Using the four channel registers from the preceding table the PSK Modulator assembles the 16 phases according to Table VII Table VII PSK Modulator Phase Phase I Value Q Value 0 0x12 0x15 1 0x13 0

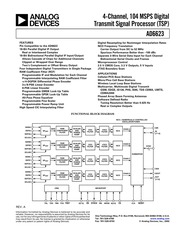

11. NCO NUMERICALLY CONTROLLED OSCILLATOR TUNER SCALER 1 SHANA gt CICS rCIC2 AND a Nco POWER FILTER FILTER RAMP RAM 1 1 COEFFICIENT a ord 5 ar 12 nco CHANB FILTER POWER FILTER FILTER d RAMP SUMMATION SCALER 1 Mane I 5 rcic2 AND a Nco POWER FILTER FILTER RAMP SCALER CHAN D Q gt cics rCIC2 AND Firer 95 9 NCO 7 POWER O TDL TDO TMS TCK TRST D 7 0 DS DTACK RW MODE 2 0 CS CLK RESET REV A Information furnished by Analog Devices is believed to be accurate and reliable However no responsibility is assumed by Analog Devices for its use nor for any infringements of patents or other rights of third parties that One Technology Way P O Box 9106 Norwood MA 02062 9106 U S A may result from its use No license is granted by implication or otherwise Tel 781 329 4700 www analog com under any patent or patent rights of Analog Devices Fax 781 326 8703 Analog Devices Inc 2002 AD6623 TABLE OF CONTENTS EEATURES kupa a ex Sipe wa e wur gr a ate aw Ie Gate e s 1 Start With Soft Sy ng ose ee AI e be eee 30 APPLICATIONS ri CENA RA ROO EXE UE A eX E a 1 Start with Pm Syne ba SSE ORR RES 30 FUNCTIONAL BLOCK DIAGRAM 1 b UU TAA SUCHE 30 PRODUCT DESC

12. SDFIB SDFOA TMS INO p OUT2 OUTO IN2 IN1 E OUT3 VDDIO VDD VDDIO VDD VDDIO VDD INA 5 OUT4 OUT6 VDD GND GND GND GND VDDIO IN3 IN5 IN7 OUT7 VDDIO GND GND GND GND VDD ING IN8 IN9 OUT9 OUT10 OUT12 VDD GND GND GND GND VDDIO IN11 IN10 J OUT11 OUT13 VDDIO GND GND GND GND VDD IN12 IN14 IN13 K OUT14 OUT17 VDD VDD VDD VDDIO IN16 IN17 IN15 L OUT16 OUT15 QIN SYNC3 M QOUT D7 D4 D1 Prices DID A1 RESET SYNC2 P NC D6 D2 DS RD A2 cs SYNC1 CLK NC NC NO CONNECT REV A 13 AD6623 196 LEAD FUNCTION DESCRIPTIONS Mnemonic Type Function POWER SUPPLY VDD P 2 5 V Supply VDDIO P 3 3 V IO Supply GND G Ground INPUTS INOUT 17 0 IO A Input Data Mantissa QIN I When HIGH Indicates Q Input Data Complex Input Mode RESET I Active LOW Reset Pin CLK I Input Clock SYNCO I All Sync Pins Go to All Four Output Channels SYNCI I Sync Pins Go to All Four Output Channels SYNC2 I All Sync Pins Go to All Four Output Channels SYNC3 I All Sync Pins Go to All Four Output Channels SDINA I Serial Data Input Channel A SDINB I Serial Data Input Channel B SDINC I Serial Data Input Channel C SDIND I Serial Data Input Channel D CS I Active LOW Chip Select CONTROL SCLKA Bidirectional Serial Clock Channel SCLKB IO Bidirectional

13. 0111 0 0197 0 0348 21 0 0035 0 0063 0 0111 0 0197 0 0348 22 0 0035 0 0063 0 0111 0 0197 0 0348 23 0 0035 0 0063 0 0111 0 0197 0 0348 24 0 0035 0 0063 0 0112 0 0197 0 0348 25 0 0035 0 0063 0 0112 0 0198 0 0348 26 0 0035 0 0063 0 0112 0 0198 0 0349 27 0 0035 0 0063 0 0112 0 0198 0 0349 28 0 0035 0 0063 0 0112 0 0198 0 0349 29 0 0035 0 0063 0 0112 0 0198 0 0349 30 0 0035 0 0063 0 0112 0 0198 0 0349 31 0 0035 0 0063 0 0112 0 0198 0 0349 32 0 0035 0 0063 0 0112 0 0198 0 0349 NUMERICALLY CONTROLLED OSCILLATOR TUNER NCO Each channel has a fully independent tuner The tuner accepts data from the CIC filter tunes it to a digital Intermediate Frequency IF and passes the result to a shared summation block The tuner consists of a 32 bit quadrature NCO and a Quadrature Amplitude Mixer QAM The NCO serves as a local oscillator and the QAM translates the interpolated channel data from baseband to the NCO frequency The worst case spurious signal from the NCO is better than 100 dBc for all output frequencies The tuner can produce real or complex outputs as requested by the shared summation block PHASE OFFSET NCO FREQUENCY WORD MICROPROCESSOR INTERFACE O CLK In the complex mode the NCO serves as a quadrature local oscillator running at fc x 2 capable of producing any frequency step between forx 4 and 6 4 with a resolution of fc 22 0 0121 Hz for 104 MHz In the real mode the NCO serves

14. Data Frame Input Channel B 117 SDFIC I Serial Data Frame Input Channel C 118 SDINB I Serial Data Input Channel B 119 SCLKC IO Bidirectional Serial Clock Channel C 120 SDFOC O Serial Data Frame Sync Output Channel C 121 SDINC I Serial Data Input Channel C 123 SCLKD IO Bidirectional Serial Clock Channel D 124 SDFOD O Serial Data Frame Sync Output Channel D 125 SDIND I Serial Data Input Channel D 126 SDFID I Serial Data Frame Input Channel D NOTES Pins with a Pull Down resistor of nominal 70 Pins with a Pull Up resistor of nominal 70 12 REV A AD6623 PIN CONFIGURATION 196 Lead CSPBGA TOP VIEW 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15mm sq BALL LEGEND Oo GROUND CORE POWER RING POWER OQ O O O O O O O O O O O O O O O O O O O O O O O O O GO O OLO O O O O O OP OOO 00000 00000 00000 00000 Q OO OQ Q O O O O O O Q O O O O O O O x O OO O O OO Or O O 0 TX 1 2 3 4 5 6 7 8 9 10 11 12 13 14 A NC SDFID SDINC SDINB SDFOB SCLKB SCLKA TDO SDFIA TCK NC B OEN SDIND SDFOC SDFIC SDINA TDI TRST SDFOD SCLKD SCLKC

15. FIR Mode COMPACT FIR M mode bit If M 0 then the MSB of 3 bit mode select word at 0xn0C 6 is set to 0 this is also called MODE 0 If M 1 then the MSB is set to 1 and this is MODE 1 Mode allows quick format changes via the serial port for example 010 GMSK and 110 3pi 8PSK The value m should be held for the duration of the time slot since the value of m will only be updated after the RCF Scale Holdoff Counter reaches a value of 1 see below S serial time slot sync bit If S 0 then no sync is generated If S 1 a Serial Time Slot Sync occurs that loads the RCF Scale Hold off Counter with a user programmed value and commences a backwards count of CLK cycles When the counter reaches one an automatic sequence occurs as follows Power Ramp Down occurs m above is updated serial input is suspended for a REST or QUIET time and any control register with a 2 superscript is updated After REST the serial input becomes active and the power level is ramped up to the Fine Scale multiplier value or any lesser power level Ramp enable bit 0xn16 0 must be set to logic 1 for the ramp functions to occur See the RCF Power Ramping andTime Slot Synchronization sections for more detail X don t care D payload data bit Important notes The sync pulse s should be held at Logic 1 for only one serial frame since every frame with Logic 1 in the s position will cause the RCF Scale Hold off Counter to reload its beginning count and b

16. Look Up Table Ox119 5 4 0 Ch A Ramp Rest Time Q 100 FIR compact mode Ox11A OxllF Reserved 101 8 PSK 0x120 0x13F 16 15 0 Ch A Data Memory 110 3n 8 8PSK Modulator 0 140 0 17 16 15 14 Reserved 13 0 Ch A Power Ramp Memory 111 QPSK Look Up Table 0x180 0x1 FF 16 15 0 Ch A Coefficient Memory 3 0 Ch A RCF Taps per Phase This address is mirrored at 0 900 0 97 Ox10D 8 7 6 RCF Coarse Scale g and contiguously extended at 00 0 dB 0x980 0x9FF 01 2 6 dB 10 2 12 dB PSK MODULATOR 11 184 The PSK MON AE an Ks s e only available when control register bit 0x000 7 is high 5 Ch A Ph Eq Enable The PSK Modulator creates 32 bit complex inputs to de 4 0 Serial Clock Divider 1 32 Interpolating FIR Filter from two or three data bits captured 0x10E 16 15 2 Ch A Unsigned Scale Factor by the serial port The FIR Filter operates exactly as if the 32 1 0 Reserved bit word came directly from the serial port There are three 0 10 18 17 16 Ch A Time Slot Sync Select PSK modulation options to choose from 7 4 DQPSK 8 PSK 00 0 See 0x001 Time Slot and 37 8 8 PSK Every symbol of any of these modulations 01 Syncl can be represented by one of the 16 phases shown in Figure 21 10 Sync2 A 11 Sync3 15 0 Ch A RCF Scale Hold Off Counter 1 Ramp Down if Ramp is enabled 2 Update Scale and Mode 3 Ramp Up if Ramp is enabled 0x110 16 15 0 Ch A RCF Phase EQ Coefl i Ox111 16 15 0

17. MSPS and an output data rate of 24x i e 92 16 MSPS which in conjunction with the 1x input rate assumes two channels used per carrier at 1 92 MSPS results in a total decimation value of 24 Since two AD6623 channels will be used for each carrier each channel will operate with a total interpolation of forty eight resulting in a total of 24 taps for the FIR filter All channels must be configured with the same FIR filter coefficients decimation and interpolation values and scaling values Configuring the AD6623 The Serial Input Data ports need run at 1 92 MSPS by using fscix 92 16 MSPS with SCLK divider 0 0x0D Bits 4 0 0 In order to properly process a UMTS channel across two channels the channels need to be synchronized The channel starts will be delayed by precise input clock periods and the NCO s will be independently phased to account for starting channels out of phase The final output summation stage adds data from separate channels together It should be noted that all serial output ports must be configured for Serial Bus Master Mode since SCLKs cannot be run at 92 16 MHz in slave mode When initiating carrier processing care should be taken to ensure that both the primary and secondary processing channels are started with precise relative timing preferably by a pulse on one of the SYNC pins The device is configured with the following filtering parameters Lacr 6 Nraps 24 Leics 8 Loc 1 1

18. Micro 7 write Addr rite Micro 6 0x02 write Byte 3 FREQ OxFF02Ye900 224 32 bits wide Q o Fh H Q 5 iQ 0x01 2 NCO FREQ amp OxFF0000 2216 write Byte 1 1 NCO FREQ gt gt 8 rite Micro 1 d1 write Byte 0 Byte 0 is written last and auses an internal write to occur FREQ amp OxFF rite 0 40 107 H p UJ K ct PS REV A AD6623 Read Pseudocode Void Read_Micro ext_address Main This code shows the reading of the NCO frequency register using the Read_Micro function defined above The variable address is the External Address A 2 0 Internal Address 0x102 channel 1 Holding registers for NCO byte wide access data int d3 d2 d1 d0 NCO frequency word write Chan Write Micro 7 write Addr Write Micro 6 0x02 read Byte 0 all data is moved from the Internal Registers to the interface registers on this access thus Byte 0 must be accessed first for the other Bytes to be valid dO Read Micro 0 amp OxFF read Byte 1 di Read Micro 1 OxFF read Byte 2 d2 Read Micro 2 amp OxFF read Byte 0 d3 Read Micro 3 amp OxFF 32 bits wide 0x01 AD6623 EVALUATION PCB ANDSOFTWARE Analog Devices offer

19. Phase word is calculated by the 8 PSK Mapper according to the following truth table Table IX 8 PSK Mapper Truth Table Serial 2 0 Sph 3 0 111b 0 011 2 010 4 000 6 001b 8 101b 10 100b 12 110b 14 37 8 8 PSK Modulation EDGE compliant 37 8 8 PSK modulation is selected by setting the channel register 6 4 to 110b The phase word is calculated according to the following diagram The three LSBs ofthe serial input word update the payload bits once per symbol The 8 PSK Mapper creates a data dependent static phase word Sph which is added to a time dependent rotating phase word Rph The 8 PSK Mapper operates exactly as described in the preceding 8 PSK Modulation section The Rph starts at zero when the RCF is reset or switches modes via a sync pulse Otherwise the Rph increments by three on every symbol 21 AD6623 SERIAL Figure 24 31 8 8 PSK Mapper MSK Look Up Table The MSK Look Up Table mode for the RCF is selected in Control Register In the MSK Mode the RCF performs arbitrary pulse shaping based on four symbols of impulse response For the MSK Mode the serial input format is 1 bit of data GMSK Look Up Table The GMSK Look Up Table mode for the RCF is selected in Control Register 0xn0C In the GMSK Mode the RCF performs arbitrary pulse shaping based on four symbols of impulse response For the GMSK Mode the serial input format is 1 Bit of data QPSK Look

20. Plastic Quad Flatpack S 128 AD6623ABC 40 C to 85 C Ambient 196 Lead CSPBGA Chip Scale Package Ball Grid Array BC 196 AD6623S PCB Evaluation Board with AD6623 and Software AD6623BC PCB CSPBGA Evaluation Board with AD6623 and Software CAUTION ESD electrostatic discharge sensitive device Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection Although the AD6623 features proprietary ESD protection circuitry permanent damage may occur on devices subjected to high energy electrostatic discharges Therefore proper ESD precautions are recommended to avoid performance degradation or loss of functionality WARNING ESD SENSITIVE DEVICE 10 REV A AD6623 PIN CONFIGURATION 128 Lead MQFP 19 ZONAS NIO ZLLNONI EONAS 9LLNONI SLLNONI LLNONI OLLNONI 6LNONI 8LNONI ZLNONI 9LNONI SLNONI LNONI OLNONI 1591 MOL 001 LOL 64 GND 63 SYNC1 62 SYNCO RE cs 59 VDD 58 AO 57 A1 56 2 55 MODE 54 GND 53 GND 52 GND TOP VIEW 51 RW WR 2 o o 2 o z 50 DTACK RDY 49 DS RD 48 DO 47 VDD 46 D1 45 D2 44 D3 43 D4 42 GND 41 VDDIO 40 05 39 G

21. RCF Interpolation 1 L h n x n k 5 This difference equation can be described by the transfer function from point b to c as N rer E apa 6 The actual implementation of this filter uses a polyphase decom position to skip the multiply accumulates when is zero Compared to the diagram above this implementation has the benefits of reducing by a factor of Lgcg both the time needed to calculate an output and the required data memory DMEM The price of these benefits is that the user must place the coefficients into the coefficient memory CMEM indexed by the interpolation phase The process of selecting the coefficients and placing them into the CMEM is broken into three steps shown below The FIR accepts two s complement I and Q samples from the serial port with a fixed point resolution of 16 bits each When the serial port provides data with less precision the LSBs are padded with zeroes The Data Mem stores the most recent 16 I and Q pairs for a total of 32 words The size of the Data Mem limits the RCF impulse response to 16 X Lacy output samples When the data words from the Serial Port have fewer than 16 bits the LSBs are padded with zeroes The Data Mem can be accessed through the Microport from 0x20 to Ox5F above the processing channel s base internal address while the channel s Prog bit is set external address 4 In order to avoid start up transients the Data Mem should

22. SCLK 92 16 AD6623 Register Configuration To process two UMTS carriers with 24x output rate the AD6623 must be properly configured The following sections describe the required register settings for this configuration Interpolation decimation and scaling values specified for the following regis ters were used to obtain the reference filter response shown in the Performance section of this data sheet Other registers may be set as needed for any individual application For registers with bit fields the following symbols are used 0 1 bit must be set to zero or one as indicated bitis dependent on the user s application but must be the same for both channels of a processing pair x bit can be set at user s discretion regardless of the channel used Coefficient Memory 0x900 0x9FF Bits 15 0 Each pair of processing channels must be assigned the same FIR filter coefficients Twenty four taps must be used typically loaded into addresses 0x900 0x9FF REV A AD6623 The FIR filter coefficients for the reference filter are 181 101 24803 2420 816 4461 14446 1729 1084 5366 1588 209 209 1588 5366 1084 1729 14446 4461 816 2420 24803 101 181 Start Sync Control Register 0xn00 Bits 17 16 The settings in this register must be the same for each pair of processing channels Start Holdoff Counter 0xn00 Bits 15 0 The secondary channel of each processing pair needs to b

23. Serial Clock Channel B SCLKC 10 Bidirectional Serial Clock Channel SCLKD IO Bidirectional Serial Clock Channel D SDFOA O Serial Data Frame Sync Output Channel A SDFOB O Serial Data Frame Sync Output Channel B SDFOC O Serial Data Frame Sync Output Channel C SDFOD Serial Data Frame Sync Output Channel D SDFIA I Serial Data Frame Input Channel SDFIB I Serial Data Frame Input Channel SDFIC I Serial Data Frame Input Channel C SDFID I Serial Data Frame Input Channel D OEN I Active High Output Enable Pin MICROPORT CONTROL D 7 0 I O T Bidirectional Microport Data A 2 0 I Microport Address Bus DS RD I Active Low Data Strobe Active Low Read DTACK RDY O T Active Low Data Acknowledge Microport Status Bit RW WR I Read Write Active Low Write MODE I Intel or Motorola Mode Select OUTPUTS OUTT117 0 O Wideband Output Data QOUT When HIGH Indicates Output Data Complex Output Mode JTAG AND BIST TRST I Test Reset Pin Active Low TCK I Test Clock Input TMS I Test Mode Select Input TDO O T Test Data Output TDI I Test Data Input NOTES 1Pins with a Pull Down resistor of nominal 70 Pins with a Pull Up resistors of nominal 70 14 REV A AD6623 CONTROL REGISTER ADDRESS NOTATION Register address notation and bit assignment referred to throughout this data sheet are as follows There are eight one digit External register addresses in decimal format

24. Summation Block section for details In this configuration intermediate OUT17s will serve as guard bits that allow intermediate sums to exceed full scale As long as the final output does not exceed 6 dB over full scale the clip detector will perform correctly If a single carrier needs to exceed 6 dB full scale hardwired scaling can be accomplished according to Table XX This is most useful when the AD6623 is processing a Single Wideband Carrier such as UMTS or CDMA 2000 Table XX Hardwired Scaling MSB Part Manufacturer LSB Max Single Connect to Clip Offset Binary Version Number ID Number Mandatory Carrier Level DAC MSB Detect Compensation 0000 0010 0111 1000 0000 000 1110 0101 1 12 04 dB OUTI7 N A Internal A BSDL file for this device is available from Analog Devices Inc 00298 gt Contact Analog Devices for more information de OUTIS only 505000 6 02 dB OUT14 only 0x0C000 SCALING Proper scaling of the wideband output is critical to maximize the spurious and noise performance of the AD6623 A relatively small overflow anywhere in the data path can cause the spurious free dynamic range to drop precipitously Scaling down the output levels also reduces dynamic range relative to an approximately constant noise floor well balanced scaling plan at each point in the signal path will be rewarded with optimum performance The scaling plan can be separated into two parts multicar

25. Up Table The QPSK Filter mode for the RCF is selected in Control Register In the QPSK Mode the RCF performs baseband linear pulse shaping based on filter impulse response up to 12 symbols For the QPSK Mode the serial input format is 1 Bit I followed by 1 Bit Q PHASE EQUALIZER The 15 95 Standard includes a phase equalizer after matched filtering at the baseband transmit side of a base station This filter pre distorts the transmitted signal at the base station in order to compensate for the distortion introduced to the received signal by the analog baseband filtering in a handset The AD6623 includes this functionality in the form of an Infinite Impulse Response IIR all pass filter in the RCF This Phase Equalizer pre distort filter has the following transfer function _ Y z _ 1 blz 6227 H z 2 X z 22 blz b2 9 Figure 25 Second Order All Pass IIR Filter The Allpass Phase Equalizer APE is enabled logic 1 or disabled logic 0 in Control Register 0 0 5 The value of Bit 5 then becomes the value of the APE term in Equation 7 The coefficients b and b are located in Control Registers 10 and 0 11 respectively The format for b and b is two s complement fractional binary with a range of 2 2 With one bit for sign at most significant bit position there are 15 bits for magnitude The value of one bit is 2 75 x 2 or 0 00006103515625 The register values in hexadecimal and the co

26. and the capabilities of the host processor See the timing diagrams for details on the operation of both modes The External Memory Map provides data and address registers to read and write the extensive control registers in the Internal Memory Map The control registers access global chip functions and multiple control functions for each independent channel Microport Control All accesses to the internal registers and memory of the AD6623 are accomplished indirectly through the use of the microprocessor port external registers shown in Table XXI Accesses to the Exter nal Registers are accomplished through the 3 bit address bus A 2 0 and the 8 bit data bus D 7 0 of the AD6623 Microport External Address 3 0 provides access to data read from or written to the internal memory up to 32 bits External Address 0 is the least significant byte and External Address 3 is the most signifi cant byte External Address 4 controls the Sleep Mode of each 34 channel External Address 5 controls the sync status of each channel External Address 7 6 determines the Internal Address selected and whether this address is incremented after subsequent reads and or writes to the internal registers EXTERNAL MEMORY MAP The External Memory Map is used to gain access to the Internal Memory Map described below External Address 7 6 sets the Internal Address to which subsequent reads or writes will be per formed The top two bits of Exter

27. be cleared before operation The Prog bit must then be reset to enable normal operation REV A The Coef Mem stores up to 256 16 bit filter coefficients The Coef Mem can be accessed through the Microport from 0x800 to Ox8FF above the processing channel s base internal address while the channel s Prog bit is set external address 4 For AD6622 compatibility the lower 128 words are also mirrored from 0x080 to OxOFF above the processing channel s base internal address while the Prog bit is set There is a single Multiply Accumulator MAC on which both the I and Q operations must be interleaved Two CLK cycles are required for the MAC to multiply each coefficient by an I and Q pair The MAC is also used for four additional CLK cycles if the All pass Phase Equalizer is active The size of the Data Mem and Coef Mem combined with the speed of the MAC determine the total number of the taps per phase Tc that may be calculated Tgcr is the number of RCF input samples that influence each RCF output sample The maximum available is calculated by the equation below 256 Lacy 2X fspro 2x an 7 Where APE 1 allpass phase equalizer enabled or 0 allpass phase equalizer disabled and fspro Output Data Rate Total Interpolation Rate in Hz floor indicates that the value within the parenthesis should be reduced to the lowest integer e g floor 9 9999 9 The impulse response length at the output o

28. bits low and PROG bits LOW 8 Write the Beam bit high and desired Sync A B C and or D bit s high at Ext Address 5 Return Beam bit to Logic 0 31 AD6623 9 This starts the Fine Scale Hold Off Counter counting down The counter is clocked with the AD6623 CLK signal When it reaches a count of one the ramp will commence from the last coefficient until it reaches the first coefficient of the specified ramp length If a Rest has been programmed Rest will commence for the programmed length and then the ramp will begin again at the first coefficient and ending at the last coefficient in the RMEM ramp memory Time Slot with Pin Sync The procedure for using the hardware synchronizing pins SYNCO 1 2 and 3 to engage the Time Slot function is very similar to the Soft Sync So for this case only the differences between the two methods will be noted It will be helpful to examine the Hardware and Software Sync Control Block Diagram Figure 37 in order to visualize the process Hardware sync pins SYNCO 1 2 and 3 are all capable of loading the Fine Scale Hold Off Counters that trigger the ramp function of any channel The SYNC pin labels do not signify attachment to specific channels but conversely each SYNC pin is routed directly or indirectly to every channel The task that the user faces is to see that the sync signal is properly routed and selected The Time Slot Sync multiplexer seen in Figure 37 is used to select a

29. can be compensated for in the RCF stage The gain should be calculated from the CIC scaling section above As an example consider an input from the RCF whose bandwidth is 0 141 of the RCF output rate centered at baseband Interpolation by a factor of five reveals five images as shown below 10 dB 1 A o 3 2 1 0 1 2 3 Figure 29 Unfiltered CIC5 Images The CIC5 rejects each of the undesired images while passing the image at baseband The images of a pure tone at channel center DC are nulled perfectly but as the bandwidth increases the rejection is diminished The lower band edge of the first image always has the least rejection In this example the CIC5 is interpolating by a factor of five and the input signal has a bandwidth of 0 141 of the RCF output sample rate The plot below shows 110 dBc rejection of the lower band edge of the first image All other image frequencies have better rejection REV A AD6623 Figure 30 Filtered CIC5 Images Table XII lists maximum bandwidth that will be rejected to various levels for CIC5 interpolation factors from 1 to 32 The example above corresponds to the listing in the 110 dB column and the Leics 5 row It is worth noting here that the rejection of the CIC5 improves as the interpolation factor increases Table XII Max Bandwidth of Rejection for Lc c Values Leics 110 dB 100 dB 90 dB 80 dB

30. edge of SCLK when in slave mode Serial Data Framing The SDIN input pin of each transmit channel of the AD6623 receives data from an external DSP to be digitally filtered inter polated and then modulated by the NCO generated carrier Serial data from the DSP to the AD6623 is sent as a series of blocks or frames The length of each block is a function of the desired output format that is supported by the AD6623 Block length may range from 1 bit MSK to 22 bits of I and Q data The flow of data to the SDIN input is regulated either by the AD6623 in Self Framing Mode or by the external DSP using AD6623 External Framing Mode This is accomplished by generating a pulse SDFO or SDFI to indicate that the next frame or serial data block is ready to be input or sent to the AD6623 Functions of the two pins SDFO and SDFI are fully described in the framing modes that follow Self Framing Mode In this mode Bit 7 of register 0xn16 is set low The serial data frame output SDFO generates a self framing data request and is pulsed high for one SCLK cycle at the input sample rate In this mode the SDFI pin is not used and the SDFO signal would be programmed to a serial data frame request 0xn16 Bit 5 0 SDFO is used to provide a sync signal to the host The input sample rate is determined by the CLK divided by channel interpo lation factor If the SCLK rate is not an integer multiple of the input sample rate then the SDFO will cont

31. ehh hh hahere hrs 21 Changes to 8 PSK Modulation section x en VAR GHI Uer er MER RR GU OO Ale Ga E E Peri d RR PR 21 Changes to 37 8 8 PSK Modulation section Z u uu rais u uk eee hh rera ahhh hrs 21 CGhang s MSK Look Up Table section cg RS Shee E Sed me tripe ee ov eee ME SET IERI oes 22 Changes to GMSK Look Up Table section s la a cee hh rera s 22 Changes to QPSK Look Up Table section yasta e REY EAE Ee X ON RE CU A as 22 Changes to PHASE EQUALIZER section oe ese rere oue eere eee RR RG ROO ie eve red REO PR DECR danas 22 Replac d Table XI zu u a aa aa RA et e AE ede actae es ect i CRIME MORES TR USES ET QA 22 Replaced SCALE AND RAMP section with FINE SCALE AND POWER RAMP section 22 New EINE SSCALINGrSeCUOD nid u reset pera ms reed ger ra met ag bee po e hq pete drame lang cna a Re laste Ide 22 New RCF POWER RAMPING section 4 255 vov ERA Ue URSUS DP Ue VAN APT e aaro REA RA E 22 Inserted new Figures 26524 preni a aus Go lea sees A TRELRUS AUS Ae A e ata ig ute ann etre ae cate RE RU e h leva ERG CA NR 23 Removed section iat ste sac els sesto S o UR CR CON ise Sor LEURS AUS RAD I REA Rat gs Pochi mA o INR 23 Changes to Figure 28 Leach RERO ace E NO e VR E

32. ensure the net gain through the CIC stages SCIC serves to frame which bits of the CIC output are transferred to the NCO stage This results in controlling the data out of the CIC stages in 6 dB increments For the best dynamic range Scc should be set to the smallest value possible lowest attenuation without creating an overflow condition This can be safely accomplished using the equation below To ensure the CIC 24 output data is in range Equation 13 must always met The maximum total interpolation rate may be limited by the amount of scaling available See ceil 4 x log 43 0 Scr lt 58 14 This polynomial fraction can be completely reduced as follows demonstrating a finite impulse response with perfect phase linearity for all values of Lcrcs 5 Lag 5 2 z X z e 15 k 0 k 1 The frequency response of the CIC5 can be expressed as follows The initial 1 factor normalizes for the increased rate which is appropriate when the samples are destined for a DAC with a zero order hold output The maximum gain is at baseband but internal registers peak in response to various dynamic inputs As long as Leics is confined to 32 or less there is no possibility of overflow at any register 5 L x si CIC5 f Locics 7 J 16 CIC5 f The pass band droop of CIC5 should be calculated using this equation and

33. operation The rCIC2 stage allows for noninteger relationships between the input data rate and the master clock This allows easier implementation of systems that are either multimode or require a clock that is not a multiple of the input data rate The overall effect is referred to as rate change A specific rate change is accomplished by choosing appropriate interpolation and decimation values for equation 17 below For example if an interpolation ratio of 2 69 is needed then set L crc2 269 and M crc2 100 Permissible Values of L cic and The two parameters that determine the rate change of the rCIC2 filter are 1 The interpolation factor L crc2 ranging from 1 to 4096 12 bits 2 The decimation factor ranging from 1 to 512 9 bits The range of L crc2 is limited by according to Table XIII Table XIII Maximum Permissible Values Chosen Value Maximum Allowed Value 1 to 22 4095 23 3836 24 3236 25 2748 26 2349 27 2020 28 1746 29 1518 30 1325 31 1162 32 1024 is restricted by equations 17 and 18 below 2 e 102 C 1 L COMPLEX 07 Where L cric2 Interpolation of rCIC2 COMPLEX Complex Output Mode off 0 on 1 2x TPP 4x 6 1 COMPLEX x Los x iu 18 rCIC2 Where TPP Taps Per Phase of RAM Coefficient Filter APE Allpass Phase Equalizer off 0 on 1 COMPLEX Com

34. or AD6623s This change in phase can be synchronized via microprocessor control or an external Sync signal To set the amplitude without synchronization the following method should be used Set Phase No Beam 1 Set the NCO Phase Offset Update Hold Off Counter 0xn05 to 0 2 Load the appropriate NCO Phase Offset 0xn04 The NCO Phase Offset will be immediately loaded Beam with SoftSync The AD6623 includes the ability to synchronize a change in NCO phase of multiple channels or chips under microprocessor control NCO Phase Offset Update Hold Off Counter in conjunction with the Beam bit and the Sync bit Ext Address 5 allow this synchronization Basically the NCO Phase Offset Update Hold Off Counter delays the new phase from being loaded into the NCO RCF by its value number of AD6623 CLKs The following method is used to synchronize a beam in phase of multiple channels via microprocessor control 1 Write the NCO Phase Offset Update Hold Off Counter 0xn05 to the appropriate value greater than 1 and less then 2191 2 Write the NCO Phase Offset register s to the new desired phase and amplitude 3 Write the Beam bit and the Sync s bit high Ext Address 5 4 This starts the NCO Phase Offset Update Hold Off Counter counting down The counter is clocked with the AD6623 CLK signal When it reaches a count of one the new phase is loaded into the NCO Beam with Pin Sync Four hardware sync pins are available on the AD662

35. should be used in the following circumstances e When driving a DAC that accepts two s complement data When driving another AD6623 in cascade mode When driving test equipment FIFO memory etc that can accept two s complement data format Output Clip Detection The MSB Bit 17 of the Wideband Output Bus is typically used as a guard bit for the purpose of clipping the wideband output bus when Bit 0 of the Summation Mode Control Register at address 0x000 is high If clip detection is enabled then Bit 17 of the output bus is not used as a data bit Instead Bit 16 will become the MSB and is connected to the MSB of the DAC Configuring the DAC in this manner gives the summation block a gain of 0 dB When clip detection is not enabled and Bit 17 is used as a data bit then the summation block will have a gain of 6 02 dB There are two data output modes The first is offset binary This mode is used only when driving offset binary DACs Two s comple ment mode may be used in one of two circumstances The first is when driving a DAC that accepts two s complement data The second is when driving another AD6623 in cascade mode When clipping is enabled the two s complement mode output bus will clip to 2 for output signals more positive than the output can express and it will clip to 0x3000 for signals more negative than the output can express In offset binary mode the output bus will clip to OX2FFFF for output signals mor

36. the channel to be sync ed in External Register address 5 allow this synchronization The RCF Fine Scale Hold Off Counter delays the beginning of the Time Slot function as well as updating the Fine Scale amplitude value if applicable The amount of time delay is set by the value number of AD6623 CLK periods written to the register at Oxn0F 15 0 Since the Time Slot event is of short duration the user should consider a digital scope set for Normal or One Shot triggering to capture the event and verify functionality The following steps are used to synchronize a Time Slot or Ramp event with a software word received through the Microport they assume that the user has established a data flow from input to output of the AD6623 1 Place the channel s in SLEEP Mode external address 4 3 0 write bit s high and in the PROG Mode external address 4 7 4 write the bit s high 2 Write the Fine Scale Hold Off Counter 0xn0F 15 0 to the appropriate value gt 1 and lt 219 1 3 Set the Ramp Enable bit 0xn16 0 high 4 Load RMEM ramp memory with up to 64 coefficients 0xn40 17F with the desired values ranging from 0 to 241 that represent the shape of the ramp transition Where 0 is zero gain and 2 1 is unity gain 5 Load the channel s ramp length minus 1 up to 63 at 0 17 6 Load the channel s ramp rest time minus 1 up to 31 at Oxn19 7 Re establish an output data flow to the DAC by bringing the channel s SLEEP

37. the composite signal if this port is unused not connected If complex data is desired there are two ways this can be obtained The first method is to simply set the QIN input of the AD6623 high and to set the Wideband Input Bus low This allows the AD6623 to output complex data on the Wideband Output Bus The I data samples would be identified when QOUT is low and the Q data samples would be identified when QOUT is high The second method of obtaining complex data is to provide a QIN signal that toggles on every rising edge of the CLK This could be obtained by connecting the QOUT of another AD6623 to QIN as shown in Figure 35 In a cascaded system the QIN of the first AD6623 in the chain would typically be tied high and the QOUT of the first AD6623 would be connected to the QIN of the following part All AD6623s will synchronize themselves to the QIN input so that the proper samples are always paired and the Wideband Output bus represents valid complex data samples Table XVI shows different parallel input and output data bus formats as a function of QIN and QOUT Table XVI Valid Output Bus Data Modes Wideband Input Output Data Type QIN IN 17 0 OUT 17 0 QOUT Low Real Real High Zero Complex Pulsed Complex Complex LOGIC1 06623 06623 IN OUT IN OUT LOGICO 17 0 17 0 17 0 16 3 Figure 35 Cascade Operation of Two AD6623s SYNCHRONIZATION Three types of synchronization can be ac

38. with optional interpolation The FIR filter can produce impulse responses up to 256 output samples long The FIR response may be interpolated up to a factor of 256 although the best filter performance is usually achieved when the RCF interpolation factor is confined to eight or below The 256 x 16 coefficient memory CMEM can be divided among an arbitrary number of filters one of which is selected by the Coefficient Offset Pointer channel address The polyphase implementation is an efficient equivalent to an integer up sampler followed FIR filter running at the interpolated rate The AD6623 RCF realizes a sum of products filter using a polyphase implementation This mode is equivalent to an inter polator followed by a FIR filter running at the interpolated rate In the functional diagram below the interpolating block in creases the rate by the RCF interpolation factor Lacp by inserting Lacr 1 zero valued samples between every input sample The next block is a filter with a finite impulse response length Ngcr and an impulse response of h n where n is an integer from 0 to Ngcr l The difference equation for Figure 20 is written below where h n is the RCF impulse response b n is the interpolated input sample sequence at point b in the diagram above and c n is the output sample sequence at point c in Figure 20 REV A AD6623 fin x Lace FIR FILTER h n Figure 20

39. 0xn02 NCO Frequency section ul usu u one ree 4 E IR ERO EROR EFI EURO e XE P rte EE eee 39 Changes to 0xnoO0F RCF Time Slot Sync section 2 0 0 eee hh herr 40 Ghanges to 0xn16 Serial Port Setup sectlon ecc e meg T UP RA Y RARE ES aM eer We ri RE Baa RE Wisa asus 40 u a arene au Saga deus GU p pec pete pce echa bip vestras en debe eed 40 Changes to 0xn40 0xn7F Power Ramp Coefficient Memory section 40 Changes to 0xn80 0xnFF Coefficient Memory section herr eher 40 Added new AD6623 EVALUATION AND SOFTWARE section sese hh hh hehe 41 Added new Figure 30 ae thn dd sateen aie ie PO PR aa ogee her SERERE ERE RN ange ER TR PR AN ARN a RH 41 Added USING THE AD6623 TO PROCESS TWO UMTS CARRIERS WITH 24x OUTPUT RATE section 44 48 REV A A 02768 0 9 02 PRINTED IN U S A

40. 3 0 Data Bytes These registers return or accept the data to be accessed for a read or write to internal addresses INTERNAL COUNTER REGISTERS AND ON CHIP RAM AD6623 and AD6622 Compatibility The AD6623 functions and programmability significantly exceed those of the AD6622 while maintaining AD6622 pin compatibil ity and functionality when desired AD6622 compatibility is selected when Bit 7 of Internal Control Register 0x000 is low In this state all AD6623 extended control registers are cleared While in the AD6622 mode the unused AD6623 pins are three stated Listed below is the mapping of internal AD6623 registers AD6622 compatibility is selected by setting 0x000 7 low In this state all AD6623 extended control registers are cleared Registers marked as Reserved must be written low Common Function Registers not associated with a particular channel Internal Address Bit AD6622 Compatible Description AD6623 Extensions Description AD6623 Extension 0 Reserved Reserved Reserved Reserved Offset Binary Outputs Clip Wideband I O First Sync Only Beam on Pin Sync Hop on Pin Sync Start on Pin Sync Ch D Sync Pin Enable Ch C Sync0 Pin Enable Ch B Sync0 Pin Enable Ch A Sync Pin Enable Unused Unused 0x000 o 0x001 0x002 0x003 O tS gt O 1 O NW BANA Ce oo AD6623 Extension 1 No Change Wideband Input Disable Dual Output Enable No Change No Chang

41. 3 to provide the most accurate synchronization especially between multiple AD6623s Synchronization of beaming to a new NCO Phase Offset with an external signal is accomplished using the following method 1 Write the NCO Phase Offset Hold Off 0xn05 Counter s to the appropriate value greater than 1 and less than 2191 2 Write the NCO Phase Offset register s to the new desired phase and amplitude 3 Set the Beam on Pin Sync bit and the appropriate Sync Pin Enable high 0xn01 4 When the Sync pin is sampled high by the AD6623 CLK this enables the count down of the NCO Phase Offset Hold Off counter The counter is clocked with the AD6623 CLK signal When it reaches a count of one the new phase is loaded into the NCO registers Time Slot Ramp This enables power ramping and allows input data format changes during the quiet period after ramp down It must be synchronized using the Microport soft sync input data or a hardware sync pin A Time Slot normally takes the form of ramp down to minimum power rest period and ramp up to maximum output power See the RCF POWER RAMPING section of this data sheet for related information The Beam soft sync signal is also routed to the Time Slot function This is a shared bit and it provides soft sync pulses to both the Phase Hold Off and Fine Scale Hold Off counters simultaneously REV A The PROG Mode bits located at External Address 4 7 4 referred to be

42. 40 pF on all outputs unless otherwise specified 3The timing parameters for SCLK SDIN SDFI SDFO and SYNC apply to all four channels A B C and D Specifications subject to change without notice REV A AD6623 MICROPROCESSOR PORT TIMING CHARACTERISTICS Test AD6623AS Parameter Conditions Temp Level Min Typ Max Unit MICROPROCESSOR PORT MODE INM MODE 0 MODE INM Write Timing tsc ControP to TCLK Setup Time Full IV 4 5 ns tuc Control to TCLK Hold Time Full IV 2 0 ns THWR WR RW to RDY DTACK Hold Time Full IV 8 0 ns tsAM Address Data to WR RW Setup Time Full IV 3 0 ns tHAM Address Data to RDY DTACK Hold Time Full IV 2 0 ns tprpy WR RW to RDY DTACK Delay Full IV 4 0 ns tacc WR RW to RDY DTACK High Delay Full IV 4Xtcik 9 ns MODE INM Read Timing tsc ControP to TCLK Setup Time Full IV 4 5 ns tuc Control to TCLK Hold Time Full IV 2 0 ns tsam Address to RD DS Setup Time Full IV 3 0 ns Address to Data Hold Time Full IV 2 0 ns tzoz Data Three State Delay Full IV ns tpp RDY DTACK to Data Delay Full IV ns tpRDY RD DS to RDY DTACK Delay Full IV 4 0 ns tacc RD DS to RDY DTACK High Delay Full IV 8Xtax 10Xtax l2Xtax ns MICROPROCESSOR PORT MOTOROLA MODE 1 MODE MNM Write Timing tsc Control to TCLK Setup Time Full IV 4 5 ns tuc Control to TCLK Hold Time Full IV 2 0 ns tups DS RD to DTACK RDY Hold Time Full IV 8 0 ns unw RW WR to DTACK RDY Hol

43. 44 45 46 48 D 7 0 Bidirectional Microport Data 49 DS RD I INM Mode Read Signal MNM Mode Data Strobe Signal 50 DTACK RDY O Acknowledgment of a Completed Transaction Signals when uP Port Is Ready for an Access Open Drain Must Be Pulled Up Externally 51 RW WR I Active HIGH Read Active Low Write 55 MODE I Sets Microport Mode MODE 1 MNM Mode MODE 0 INM Mode 56 57 58 A 2 0 I Microport Address Bus 60 CS I Chip Select Active low enable for uP Access 61 RESET I Active Low Reset Pin 62 SYNCO I SYNC Signal for Synchronizing Multiple AD6623s 63 SYNCI I SYNC Signal for Synchronizing Multiple AD6623s 67 CLK I Input Clock 69 SYNC2 I SYNC Signal for Synchronizing Multiple AD6623s 70 QIN I When HIGH indicates Q input data Complex Input Mode 71 74 77 79 82 86 89 91 94 97 INOUTT 17 0 Wideband Input Output Data Allows Cascade of Multiple AD6623 Chips In a System 73 SYNC3 I SYNC Signal for Synchronizing Multiple AD6623s 100 TRST I Test Reset Pin 101 TCK I Test Clock Input 105 SDFIA I Serial Data Frame Input Channel A 106 TMS I Test Mode Select 107 TDO O Test Data Output 108 TDI 1 Test Data Input 109 SCLKA IO Bidirectional Serial Clock Channel 111 SDFOA Serial Data Frame Sync Output Channel 112 SDINA I Serial Data Input Channel A 113 SCLKB IO Bidirectional Serial Clock Channel 114 SDFOB O Serial Data Frame Sync Output Channel B 115 SDFIB I Serial

44. 623 CLKs The following method is used to synchronize a hop in frequency of multiple channels via microprocessor control 1 Write the NCO Frequency Hold Off 0xn03 counter to the appropriate value gt 1 and lt 2191 2 Write the NCO Frequency register s to the new desired frequency 3 Write the Hop bit and the Sync s bit high Ext Address 5 4 This starts the NCO Frequency Hold Off counter counting down The counter is clocked with the AD6623 CLK signal When it reaches a count of one the new frequency is loaded into the NCO Hop with Pin Sync Four hardware Sync pins are available on the AD6623 to pro vide the most accurate synchronization especially between multiple AD6623s Synchronization of hopping to a new NCO frequency with an external signal is accomplished with the fol lowing method 1 Write the NCO Frequency Hold Off Counter s 0xn03 to the appropriate value greater than 1 and less than 2191 2 Write the NCO Frequency register s to the new desired frequency 3 Set the Hop on Pin Sync bit and the appropriate Sync pin Enable high 0xn01 4 When the Sync pin is sampled high by the AD6623 CLK this enables the count down of the NCO Frequency Hold Off Counter The counter is clocked with the AD6623 CLK signal When it reaches a count of one the new frequency is loaded into the NCO REV A AD6623 Beam A change in phase for a particular channel and can be synchronized with respect to other channels

45. 70 dB 1 Full Full Full Full Full 2 0 101 0 127 0 160 0 203 0 256 3 0 126 0 159 0 198 0 246 0 307 4 0 136 0 170 0 211 0 262 0 325 5 0 136 0 175 0 217 0 269 0 333 6 0 143 0 178 0 220 0 282 0 337 7 0 144 0 179 0 222 0 275 0 340 8 0 145 0 180 0 224 0 276 0 341 9 0 146 0 181 0 224 0 277 0 342 10 0 146 0 182 0 225 0 278 0 343 11 0 147 0 182 0 226 0 278 0 344 12 0 147 0 182 0 226 0 279 0 344 13 0 147 0 183 0 226 0 279 0 345 14 0 147 0 183 0 226 0 279 0 345 15 0 148 0 183 0 227 0 280 0 345 16 0 148 0 183 0 227 0 280 0 345 17 0 148 0 183 0 227 0 280 0 346 18 0 148 0 183 0 227 0 280 0 346 19 0 148 0 183 0 227 0 280 0 346 20 0 148 0 184 0 227 0 280 0 346 21 0 148 0 184 0 227 0 280 0 346 22 0 148 0 184 0 227 0 280 0 346 23 0 148 0 184 0 227 0 280 0 346 24 0 148 0 184 0 227 0 280 0 346 25 0 148 0 184 0 227 0 281 0 346 26 0 148 0 184 0 227 0 281 0 346 27 0 148 0 184 0 227 0 281 0 346 28 0 148 0 184 0 227 0 281 0 346 29 0 148 0 184 0 227 0 281 0 346 30 0 148 0 184 0 227 0 281 0 346 31 0 148 0 184 0 227 0 281 0 346 32 0 148 0 184 0 228 0 281 0 346 REV A THE rCIC2 RESAMPLING INTERPOLATION FILTER The rCIC2 filter is a second order re sampling Cascaded Inte grator Comb filter whose impulse response is defined by its rate change factors L crc2 and 2 The rcc filter is imple mented using a technique that does not require a faster clock than the output rate thus simplifying design and saving power while maintaining jitter free

46. 76 8MSPS 76 8 MSAMPLES SEC SUMMATION 76 8MSPS Figure 40 Driving Multiple TSP Serial Ports from 0 Hz to 7 68 MHz X Lrcr Nrsp The composite RCF and CIC frequency response is shown in Figure 44 on the same frequency scale This figure demonstrates a good approximation to a root raised cosine with a roll off factor of 0 22 a passband ripple of 0 1 dB and stopband ripple better than 70 dB until the lobe of the first image which peaks at 60 dB about 7 68 MHz from the carrier center This lobe could be reduced by shifting more of the interpolation towards the RCF but that would sacrifice near in performance As shown the first image can be easily rejected by an analog filter further up the signal path Scaling must be considered as normal with an interpolation factor of L to guarantee no overflow in the RCF CIC or NCOs The output level at the summation port should be calculated using an interpolation factor of L Nrsp Programming Multiple TSPs Configuring the TSPs for de interleaved operation is straight forward All the Channel Registers and the CMEM of each TSP are programmed identically except the Start Hold Off Counters and NCO Phase Offset In order to separate the input timing to each TSP the Hold Off Counters must be used to start each TSP successively in response to a common Start SYNC The Start SYNC may originate from the SYNC pin or the Microport Each subsequent TSP must have a Hold Off Cou

47. ANALOG 4 Channel 104 MSPS Digital DEVICES Transmit Signal Processor TSP AD6623 FEATURES Digital Resampling for Noninteger Interpolation Rates Pin Compatible to the AD6622 NCO Frequency Translation 18 Bit Parallel Digital IF Output Carrier Output from DC to 52 MHz Real or Interleaved Complex Spurious Performance Better than 100 dBc 18 Bit Bidirectional Parallel Digital IF Input Output Separate 3 Wire Serial Data Input for Each Channel Allows Cascade of Chips for Additional Channels Bidirectional Serial Clocks and Frames Clipped or Wrapped Over Range Microprocessor Control Two s Complement or Offset Binary Output 2 5 V CMOS Core 3 3 V Outputs 5 V Inputs Four Independent Digital Transmitters in Single Package JTAG Boundary Scan RAM Coefficient Filter RCF Programmable IF and Modulation for Each Channel Stati Programmable Interpolating RAM Coefficient Filter Mi 4 Pl C ilie pees 7 4 DOPSK Differential Phase Encoder FIDE base Stations 3 8 PSK Linear Encoder Wireless Local Loop Base Stations 8 PSK Linear Encoder Multicarrier Multimode Digital Transmit Programmable GMSK Look Up Table CMT 15136 PHS 1595 TDS CDMA UMTS Programmable QPSK Look Up Table All Pass Phase Equalizer Programmable Fine Scaler Programmable Power Ramp Unit High Speed CIC Interpolating Filter Phased Array Beam Forming Antennas Software Defined Radio Tuning Resolution Better than 0 025 Hz Real or Complex Outputs FUNCTIONAL BLOCK DIAGRAM

48. C2 is interpolating by a factor of five and the input signal has a bandwidth of 0 0033 of the CIC5 output sample rate Figure 32 shows 110 dBc rejection of the lower band edge of the first image All other image frequencies have better rejection Figure 32 Filtered rCIC2 Images Table XIV lists maximum bandwidth that will be rejected to various levels for CIC2 interpolation factors from 1 to 32 The example above corresponds to the listing in the 110 dB column and the L cic2 5 row The rejection of the CIC2 improves as the interpolation factor increases REV A AD6623 Table XIV Maximum Bandwidth of Rejection for Values 104 100dB 90dB 80dB 70 dB 1 Full Full Full Full Full 2 0 0023 0 0040 0 0072 0 0127 0 0226 3 0 0029 0 0052 0 0093 0 0165 0 0292 4 0 0032 0 0057 0 0101 0 0179 0 0316 5 0 0033 0 0059 0 0105 0 0186 0 0328 6 0 0034 0 0060 0 0107 0 0189 0 0334 7 0 0034 0 0061 0 0108 0 0192 0 0338 8 0 0035 0 0062 0 0109 0 0193 0 0341 9 0 0035 0 0062 0 0110 0 0194 0 0343 10 0 0035 0 0062 0 0110 0 0195 0 0344 11 0 0035 0 0062 0 0110 0 0195 0 0345 12 0 0035 0 0062 0 0111 0 0196 0 0346 13 0 0035 0 0062 0 0111 0 0196 0 0346 14 0 0035 0 0063 0 0111 0 0196 0 0346 15 0 0035 0 0063 0 0111 0 0197 0 0347 16 0 0035 0 0063 0 0111 0 0197 0 0347 17 0 0035 0 0063 0 0111 0 0197 0 0347 18 0 0035 0 0063 0 0111 0 0197 0 0348 19 0 0035 0 0063 0 0111 0 0197 0 0348 20 0 0035 0 0063 0

49. C2 provides fractional rate interpolation from 1 to 4096 in steps of 1 512 The wide range of interpolation factors in each CIC filter stage and a highly flexible resampler incorporated into rCIC2 makes the AD6623 useful for creating both narrowband and wideband carriers in a high speed sample stream The high resolution 32 bit NCO allows flexibility in frequency planning and supports both digital and analog air interface standards The high speed NCO tunes the interpolated complex signal from the rCIC2 to an IF channel The result may be real or complex Multicarrier phase synchronization pins and phase offset registers allow intelligent management of the relative phase of independent RF channels This capability supports the requirements for phased array antenna architectures and man agement of the wideband peak power ratio to minimize clipping at the DAC The wideband Output Ports can deliver real or complex data Complex words are interleaved into real I and imaginary Q parts at half the master clock rate AD6623 SPECIFICATIONS RECOMMENDED OPERATING CONDITIONS Test AD6623 Parameter Level Min Typ Max Unit VDD IV 2 25 2 5 2 75 V VDDIO IV 3 0 3 3 3 6 V Parameter Conditions Temp Test Level Min Typ Max Unit LOGIC INPUTS 5 V TOLERANT Logic Compatibility Full 3 3 V CMOS Logic 1 Voltage Full IV 2 0 5 0 V Logic 0 Voltage Full IV 0 3 0 8 V Logic 1 Current Full

50. CF modes and input data format that it sets Table I Serial Data Format Oxn0C Oxn0C Oxn0C Serial Data RCF Bit6 Bit 4 Word Length Mode 0 0 0 32 FIR 0 4 5 0 1 0 GMSK 0 1 1 MSK 1 0 0 24 Bit 9 is high FIR 16 Bit 9 is low compact 1 0 1 8 PSK 1 1 0 37 8 8 PSK 1 1 1 QPSK The serial data input SDIN accepts 32 bit words as channel input data The 32 bit word is interpreted as two 16 bit two s comple ment quadrature words I followed by Q MSB first This results in linear I and Q data being provided to the RCF The first bit is shifted into the serial port starting on the next rising edge of SCLK after the SDFO pulse Figure 16 shows a timing diagram for SCLK master SCS 0 and SDFO set for frame request SFE 0 CLK tsspio CLKn tosprooa isspio XXXXXXXXXXX XX Figure 16 Serial Port Switching Characteristics As an example of the Serial Port operation consider a CLK frequency of 62 208 MHz and a channel interpolation of 2560 In that case the input sample rate is 24 3 kSPS 62 208 MHz 2560 which is also the SDFO rate Substituting fsci 2 32 3 into the equation and solving for SCLKdivider we find the minimum value for SCLKdivider according to the equation below 32 3 Evaluating this equation for our example SCLKdivider must be less than or equal to 79 Since the SCLKdivider channel register is a 5 bit unsigned nu

51. E 22 0xn0D Channel Mode Control 2 40 FINE SCALE AND RAMP 22 xnOB Eie Scale Pact t cues saus EUR CAESA EE ew m ck 40 FINE SCALING kae orders tes 22 OxnOF RCF Time Slot Sync 40 RCF POWER RAMPING case ccs ase cme news DH Re 22 0 10 0 11 RCF Phase Equalizer Coefficients 40 Ramp Triggering a aka oa ees aches hou ers RE RI X CAE RUE 23 0xn12 0xn15 FIR PSK Magnitudes 40 Special Handling for SYNCO 23 0 10 Serial Port Setup eee OSG ae Rack 6 E 40 CASCADED INTERGRATOR COMB CIC 0xn17 Power Ramp Length 0 40 INTERPOLATING FILTERS 24 0xn18 Power Ramp Length 1 40 CIC Scaling vrss odes Por re core cR OR bare Rad CAI 24 0xn19 Power Ramp Rest Time 40 Tal cone sale a BUTI ace QURE Bue ac uma aen au basu 24 xn20 OxnlB Unused cesse n EE OO E OCA 40 The rCIC2 RESAMPLING INTERPOLATION FILTER 25 0xn20 0xn3F Data Memory 40 Permissible Values of L crc2 and 25 0xn40 0xn17F Power Ramp Coef

52. IC2 Decimation M 1 0x108 11 8 Reserved Ch A CCI2 Interpolation L 1 extended 7 0 Ch A C1C2 Interpolation L 1 No Change 0x109 7 0 Ch A C1C5 Interpolation L5 1 No Change 0x10A 15 8 Reserved Ch A RCF TapsB Nace 1 8 bits 7 Reserved Ch A TapsA Nacr 1 new MSB 6 0 Ch TapsA 1 7 bits No Change 0x10B 7 Reserved Ch A RCF Coef Offset new MSB 6 0 Ch A Coefficient Offset Ogcg 7 bits No Change 0x10C 15 10 Unused Reserved 9 Unused Ch A Compact FIR Input Word Length 0 16 bits 8 I followed by 8 Q 1 24 bits 12 I followed by 12 Q 8 Unused Ch A RCF PRBS Enable 7 Ch A PRBS Length Ch A RCF PRBS Length 0 15 0 15 1 8 388 607 1 8 388 607 6 Ch A RCF PRBS Enable Ch A RCF Mode Select 1 of 3 5 Ch Mode Select 1 of 2 Ch A RCF Mode Select 2 of 3 4 Ch A RCF Mode Select 2 of 2 Ch A RCF Mode Select 3 of 3 00 FIR 000 FIR 01 FIR 001 7 4 DQPSK 10 QPSK 010 GMSK 11 MSK 011 MSK 100 FIR Compact Input Resolution 101 8 PSK 110 31 8 8PSK 111 QPSK 3 0 Ch Taps per Phase 12 No Change 0x10D 7 6 Ch A RCF Coarse Scale a No Change 00 0 dB 01 6 dB 10 12 dB 11 18 dB 5 Ch A RCF Phase EQ Enable No Change 4 0 Ch A Serial Clock Divisor 2 4 64 Ch A Serial Clock Divisor 1 2 32 0 10 15 Ch A Serial Fine Scale Factor Enable Ch A Unsigned Scale Factor This is extended to allow values in the range 0 2 14 2 C

53. IV 1 10 uA Logic 0 Current Full IV 0 10 uA Input Capacitance 25 C V 4 pF LOGIC OUTPUTS Logic Compatibility Full 3 3 V CMOS TTL Logic 1 Voltage 0 25 mA Full IV 2 0 VDD 0 2 V Logic 0 Voltage 0 25 mA Full IV 0 2 0 4 V IDD SUPPLY CURRENT GSM Example CORE V 232 mA IO 56 mA IS 136 Example CORE V 207 mA IO 55 mA WBCDMA Example V TBD mA Sleep Mode Full IV TBD mA POWER DISSIPATION GSM Example V 740 mW IS 136 Example V 700 mW WBCDMA Example V TBD mW Sleep Mode Full IV TBD mW See the Thermal Management section of the data sheet for further details 4 REV A GENERAL TIMING CHARACTERISTICS AD6623 Test AD6623AS Parameter Conditions Temp Level Min Typ Max Unit CLK Timing Requirements Full I 9 6 ns tcrkr CLK Width Low Full IV 3 ns tcrkH CLK Width High Full IV 3 0 5 ns RESET Timing Requirement TRESL RESET Width Low Full I 30 0 ns Input Data Timing Requirements tsr INOUT 17 0 QIN to TCLK Setup Time Full IV 1 ns tur INOUTT 17 0 QIN to TCLK Hold Time Full IV 2 ns Output Data Timing Characteristics tpo TCLK to OUT 17 0 INOUT 17 0 QOUT Output Delay Time Full IV 2 6 ns tpzo OEN HIGH to OUTT 17 0 Active Full IV 3 7 5 ns SYNC Timing Requirements tss SYNC 0 1 2 3 to TCLK Setup Time Full IV 1 05 tus SYNC 0 1 2 3 to TCLK Hold Time Full IV 2 ns Master Mode Serial Port Timing Requirements SCS 0

54. Internal address notation read from left to right begins with Ox meaning the address that follows is hexadecimal The next three characters represent the address The first number or character is the MSB of the address If an n is present its value can be 1 2 3 or 4 and it depends upon the channel that is being addressed A B C or D The remaining two digits preceding the colon if present are the LSBs of the address If a colon follows the address then the succeeding digits tell the user what bit number s is are involved in decimal format For example 0xn24 7 0 SERIAL DATA PORT The AD6623 has four independent Serial Ports A B C and D and each accepts data to its own channel A B C or D of the device Each Serial Port has four pins SCLK Serial CLocK SDFO Serial Data Frame Out SDFI Serial Data Frame In and SDIN Serial Data INput SDFI and SDIN are inputs SDFO is an output and SCLK is either input or output depending the state of SCS Serial Clock Slave 0xn16 Bit 4 Each channel can be operated either as a Master or Slave channel depending upon SCS The Serial Port can be self framing or accept external framing from the SFDI pin or from the previous adjacent channel 0 16 Bits 7 and 6 Serial Master Mode SCS 0 In master mode SCLK is created by a programmable internal counter that divides CLK When the channel is sleeping SCLK is held low SCLK becomes active on the fir

55. MIGROPORT CONTROL 14 External Address 3 0 Data Bytes 36 OUTPUTS eet bre e RODA V Seam er ORA US 14 INTERNAL CONTROL REGISTERS AND ON CHIP RAM 36 JTAG AND BIST ei hdd nae sda X e E d 14 AD6623 and AD6622 Compatibility CONTROL REGISTER ADDRESS NOTATION 15 Common Function Registers not associated with a particular channel 36 SERIAL DATA PORT pde RR EXON 15 Channel Function Registers 0x1xx Ch A Serial Master Mode SCS 0 15 Ch B 0x3xx Ch C Ch D 36 Serial Slave Mode SCS lY AT RE xp RU 15 0x000 Summation Mode Control 38 Data Framing eee es pA RG eec KO 15 0x001 Sync Mode Control uu uke Pesce 44 ASR 38 Self Framing eee ay hee RARO ALS RA 15 0x002 BIST Counter z l usasqa ac des Rm e eed 38 External Framing Mode zu ere E ERE ode owe en RUE Ree 15 0x003 BIST Result usa MEE Rx ES ROUTE KOREAN ER Y 38 Serial Port Cascade Configuration 15 0xn00 Start Update Hold Off Counter 39 serial Data ce me en e DO ROME tel RE Poon 16

56. ND GND 103 VDD 104 SDFIA 105 TMS 106 TDI 108 TDO 107 SCLKA 109 VDDIO 110 SDFOA 111 SDINA 112 SCLKB 113 SDFOB 114 SDFIB 115 GND 116 SDFIC 117 SDINB 118 SCLKC 119 SDFOC 120 SDINC 121 VDDIO 122 SCLKD 123 SDFOD 124 SDIND 125 SDFID 126 VDD 127 GND 128 e I wli col si wielrellellej LO 2 ba Kas Gc Bs 0 cl ic SN est ES EEEE 9a aNd and 1noo 21110 9 110 LLno eLino LLLNO and OLLNO 61no 81no 4400 91no sino vino 1 1 Lino and aNd 11 REV A AD6623 128 LEAD FUNCTION DESCRIPTIONS Pin Number Mnemonic Type Description 1 3 5 9 19 21 31 32 34 36 38 39 GND P 42 52 54 64 65 68 72 83 85 95 96 98 99 102 103 116 128 2 OEN I Active High Output Enable Pin 29 28 27 25 24 23 22 18 17 16 15 OUT 17 0 O T Parallel Output Data 13 12 11 10 8 7 6 Ground Connection 47 59 66 104 127 VDD 2 5 V Supply 14 26 41 78 90 110 122 VDDIO P 3 3 V Supply 30 QOUT O T When HIGH indicates Q Output Data Complex Output Mode 33 37 40 43

57. R qe 24 Replaced Table XM i mdi pb ue S e WEA a ALERTE E VM ed e AAS a E US Lees Eb e Rd 25 Changes to Table Ba UAR Rar ble Rete Cede P PLNS See Te cane 25 Inserted new THE rCIC2 RESAMPLING INTERPOLATION FILTER section seeeeeee I e 25 R placed Equation 17 AWE eee ere HEY m eise e SU Ree eR enn ren E 25 Added Frequency Response of rCIC2 heading een hh hh 26 Added Programming Guidelines for AD6623 CIC Filters heading 1 ccc eee eee nent eee hern 26 Gh rnges to Table XIV Sarana tas UE M DER NR RE ei eee D ieu EVEN P EM EE 27 Changes to NUMERICALLY CONTROLLED OSCILLATOR TUNER section 27 Added Dual 18 Bit Output Configuration heading eee hh hahere a hr 28 Added Output Data Format heading uu L css fits as tees pm ih harka RD Ra Fel dex e Reime Ie E EU KH Qar haya 28 Added textto Output Data Format sectio ese ve un er RERO eR eer e oe dae LE Gr ME RT 28 Added O tput Clip Detection heading ua sua pu aaa RENE UP ROW dor uUi EQ PUN USANDO 28 Added Cascading Multiple AD6623s heading heh hh ra herren 28 Added Selection of Real and Complex Output Data Types heading ene ene nent ene hn 29 Added Hold Off Counter

58. RCF Coarse Scale dB 0 0 0 1 6 0 12 1 18 Bit 5 Bits 4 0 High enables the RCF phase equalizer Sets the serial clock divider SDIV that determines the serial clock frequency based on the following equation CLK Spry 1 0xn0E Fine Scale Factor 29 Bits 15 2 Sets the RCF Fine Scale Factor as an unsigned number representing the values 0 2 This register is shad owed for synchronization purposes The shadow can be read back directly the Fine Scale Factor can not Bits 1 0 Reserved 0xn0F RCF Time Slot Sync Bits 17 16 The Time Slot Sync Select bits are used to set which sync pin will initiate a time slot sync sequence The Fine Scale Hold Off Counter is used to syn chronize the change of RCF Fine Scale See the Synchronization section for a detailed explanation If no synchronization is required this register should be set to 0 0xn10 0xn11 RCF Phase Equalizer Coefficients See the RCF section for details 0xn12 0xn15 FIR PSK Magnitudes See the RCF section for details Bits 15 0 0xn16 Serial Port Setup Bits 7 6 Serial Data Frame Start Select Table XXV Serial Port Setup Bit 7 Bit 6 Serial Data Frame Start 0 X Internal Frame Request 1 0 External SDFI Pad 1 1 Previous Channels Frame End Bit 5 High means SDFO is a frame end low means SDFO is a frame request Bit 4 High selects serial slave mode SCLK is an input in serial slave mode

59. RCF filter Recalling the maximum equation from the RCF description are three restrictions to the RCF impulse response length Time Restriction CMEM Restriction amp mi 7 16x 236 32 4 DMEM Restriction where L X Lors X Loc _ Nrsp X 33 Jin De interleaving the input data into multiple TSPs extends the time restriction and may possibly extend the DMEM restriction but will not extend the CMEM restriction De interleaving the input stream to multiple TSPs divides the input sample rate to each TSP by the number of TSPs used Nysp To keep the output rate fixed L must be increased by a factor of which extends the time restriction This increase in L may be achieved by increasing any one or more of Lgcr Leics or Lcrc2 within their normal limits Achieving a larger L by increasing Lacy instead of Leics or Lcic2 will relieves the DMEM restriction as well In a UMTS example Nrsp 4 76 8 MHz and fn 3 84 MHz resulting in L 80 Factoring L into 10 Loic 8 and 1 results in a maximum 40 due to the time restriction Figure 42 shows an example RCF impulse response which has a frequency response as shown in Figure 43 REV A AD6623 RAM COEF FILTER DATA RE FORMATTER FILTER COMPLEX SIGNAL 32 BITS 16 I 16 Q 3 REAL OR IMAGINARY SIGNAL 9 6MSPS 9 6MSPS

60. RIPTION E ERE RE RM 3 Ser Prequency No Hop al u e mk pce Ra eon s 30 FUNCTIONAL OVERVIEW 3 Hop with SoftSyne usya a 30 RECOMMENDED OPERATING CONDITIONS 4 Pin Sync e pex ere ROC E E COE 30 ELECTRICAL CHARACTERISTICS 4 aaa eau qe edam deseen 31 LOGIC INPUTS 5 V TOLERANT 4 Set Phase No sw eR ad uqa 31 LOOIC OUTPUTS ii BERENS S Ee p Ed eR das 4 Beam with SoS Me was ye ek hh ex PKU EWE LEAR susu RR MESE EAE 31 IDD SUPPLY CURRENT ein x IU REX noe E ERREN EEA 4 Bini with Pin Syne vagiar or ee eines Fit ee rb ele n s 31 POWER DISSIPATION aa his Ree 4 Time Slot Ramp s uite taba rete eC FIA 31 GENERAL TIMING CHARACTERISTICS 5 Set Output Power No Ramp 31 MICROPROCESSOR PORT TIMING CHARACTERISTICS 6 Time Slot Ramp with SoftSync 31 MICROPROCESSOR PORT MODE INM MODE 0 6 Time Slot with Pin Syne ree E ewe bees 32 MICROPROCESSOR PORT MOTOROLA MODE 1 6 JTAG INTERFACE EX AREE Pee Mea 33 TIMING DIAGRAMS ik gas usakuy aa mi edere

61. The NCO Frequency contains a shadow register for synchronization purposes The NCO frequency can be read back directly however the shadow register cannot CLK NCO output frequency should not exceed approximately 45 of the CLK This makes allowance for the image filtering after D A conversion 0xn03 NCO Frequency Update Hold Off Counter See the Synchronization section for detailed explanation If no synchronization is required this register should be set to 0 Bits 17 16 The Hop Sync Select bits are used to set which sync pin will initiate a hop sequence Bits 15 0 The Hold Off Counter is used to synchronize the change of NCO frequencies 0xn04 NCO Phase Offset This register is 16 bit unsigned integer that is added to the phase accumulator of the NCO This allows phase synchronization of multiple channels of the AD6623 s The NCO Phase Offset contains a shadow register for synchronization purposes The shadow can be read back directly the NCO Phase Offset cannot See the Synchronization section for details 0xn05 NCO Phase Offset Update Hold Off Counter See the Synchronization section for a detailed explanation If no synchronization is required this register should be set to 0 Bits 17 16 The Phase Sync Select bits are used to set which sync pin will initiate a phase sync sequence gece 232 x JCHANNEL 27 Bits 15 0 The Hold Off Counter is used to synchronize the change of NCO phase

62. Y Figure 37 Block Diagram of Hardware and Software Sync Control for One AD6623 Sync Channel 32 REV A AD6623 JTAG INTERFACE The AD6623 supports a subset of IEEE Standard 1149 1 specifica tion For additional details of the standard please see IEEE Standard Test Access Port and Boundary Scan Architecture TEEE 1149 publication from IEEE The AD6623 has five pins associated with the JTAG interface These pins are used to access the on chip Test Access Port and are listed in Table XVII Table XVII Test Access Port Pins Name Pin Number Description TRST 100 Test Access Port Reset TCK 101 Test Clock TMS 106 Test Access Port Mode Select TDI 108 Test Data Input TDO 107 Test Data Output Note that TCK and TDI are internally pulled down which is opposite of IEEE Standard 1149 1 These pins may be connected to external pull up resistors with the associated additional current draw through the pull ups or left unconnected The AD6623 supports four op codes are shown in Table XVIII These instructions set the mode of the JTAG interface Table XVIII Op Codes Instruction Op Code IDCODE 10 BYPASS 11 SAMPLE PRELOAD 01 EXTEST 00 The Vendor Identification Code Table XIX can be accessed through the IDCODE instruction and has the following format Table XIX Vendor Identification Code phase offsets Nevertheless in most cases with a large number of carriers the worst case peak is an unlik